I've got a few ADS1158s on a custom board, and they're mostly working. Due to a pin-mapping error, the only way I can read data from them utilizing the channel read data command in Auto-scan mode.

I've configured the ADC to be as fast as possible, by setting DLY = 000 and DRATE to 11. According the datasheets table, this configuration should give me 23,739 samples / sec.

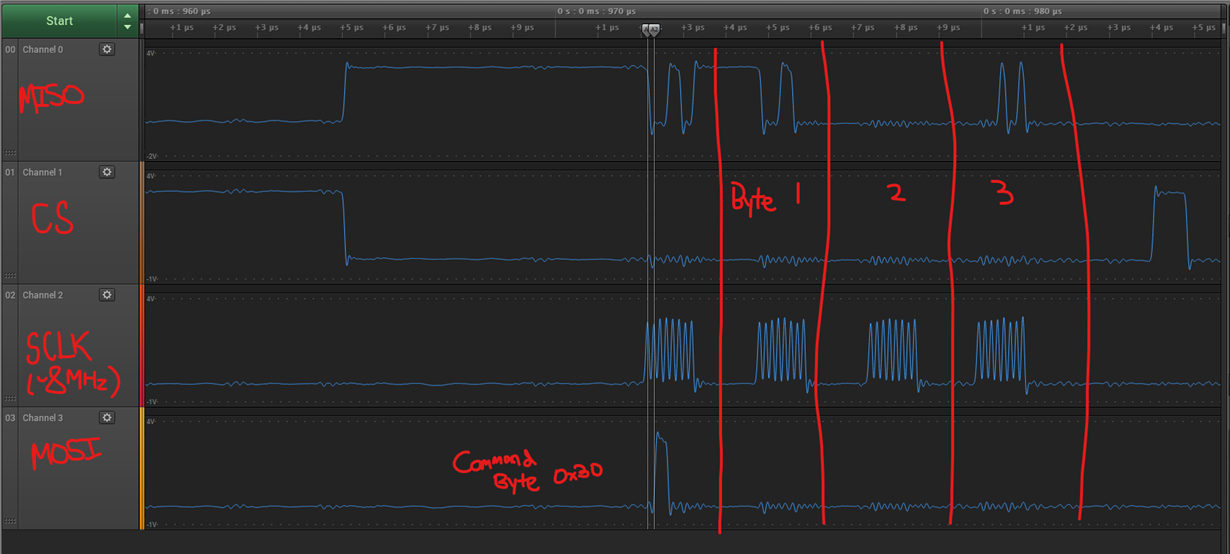

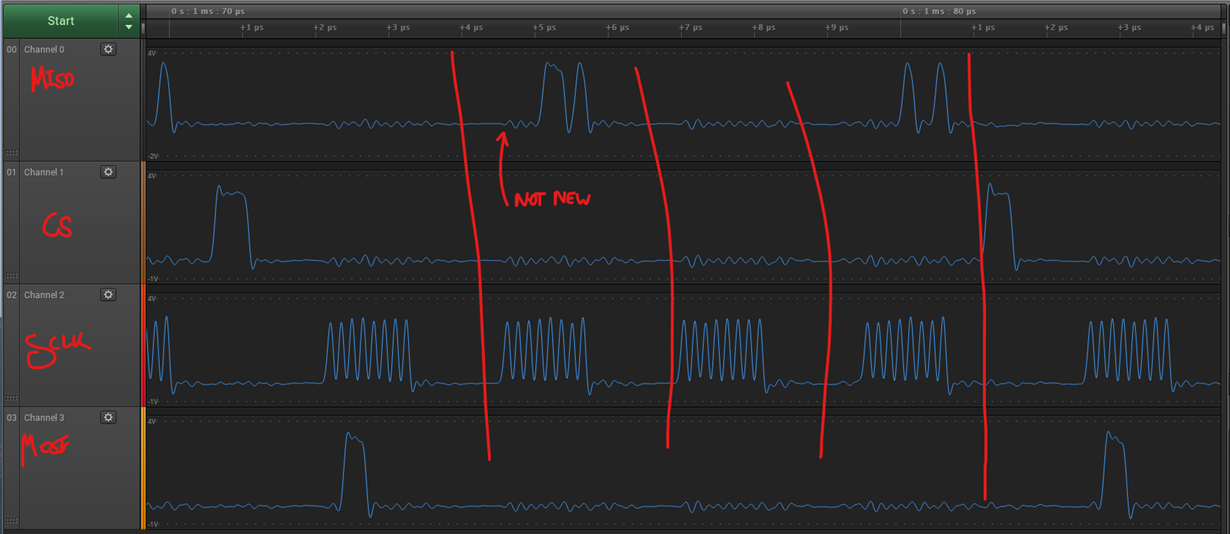

I thought that the limiting factor of the data read/transfer rate would just be the speed of the SPI bus. However, the MCU is requesting about 12,500 samples per second and 75% (about 8,400) of the returned data are not marked as "new" data (bit #7 of the first returned byte). So it seems the ADC is reading in data much slower than expected.

I'm initializing the ADS1158 to sample as fast as possible, and am reading in all configuration registers to double-check that they're properly configured. I've also measured the external oscillator frequency to verify that they're outputting the proper frequency of 32Khz - which they are.

I've poured over the datasheet, trying to figure out if I'm missing something but I haven't been able to find anything. What could be the problem here? Is there something I'm missing?