Other Parts Discussed in Thread: LMK04828

Good day to all!

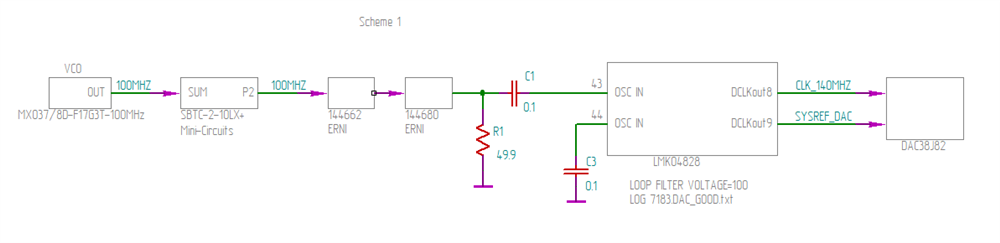

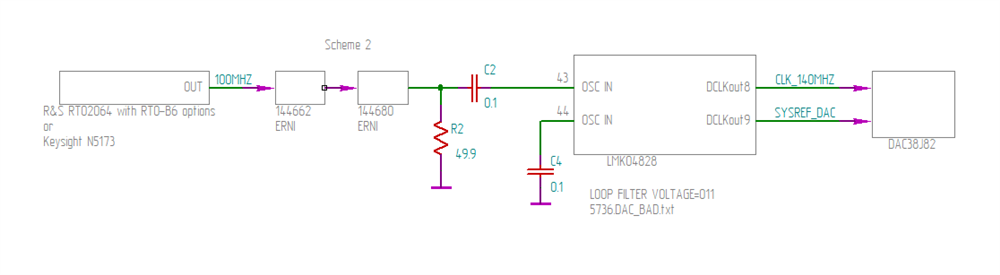

We use the DAC38J82 and it works fine, but sometimes the DAC PLL is out of lock.

When reading the DAC registers, the difference is only in the memin_pll_lfvolt (config49), if everything works fine then it is 100, if the problem is with the DAC PLL then it is 011.

Both values memin_pll_lfvolt are valid. What could be the problem that the DAC PLL is out of lock?

I attached two files with DAC registers. DAC_GOOD.txt - DAC works correctly, DAC_BAD.txt - when DAC PLL is out of lock.

80A11800 81000300 82208200 83F00000 84FFFF00 85FF0700 86FFFF00 87230000 88049300 891F0000 8A000000 8B000000 8C030000 8D030000 8E040000 8F040000 90000000 91000000 92000000 93000000 94000000 95000000 96000000 97000000 98000000 99000000 9A000000 9B340800 9E999900 9F998000 A0800800 A21B1100 A301FF00 A4003000 A5200000 A6000000 AD000100 AEFFFF00 AF000400 B0000000 B1040400 B2072000 B3E41000 B4000000 BB980000 BC805000 BD008800 BE010800 BF000000 C1000000 C2000000 C3000000 C4000000 C6004400 C719C800 C8314300 C9000000 CA032100 CB080100 CC090100 CD010000 CE0F0F00 CF1C4100 D0000000 D100DF00 D200FF00 D3000000 D400FF00 D500FF00 D6000000 D700FF00 D800FF00 D9000000 DA00FF00 DB00FF00 DC113300 DE000000 DF012300 E0576400 E1021100 E4000000 E5000000 E64F0F00 E7FF0F00 E8FF0F00 E9FB0B00 EAFF0E00 EBF30D00 EC000600 ED00F000 EE000000 EF000000 F0000000 F1000000 F2000000 F3000000 F4000000 F5000000 F6000000 F7000000 F8000000 F9000000 FA000000 FB000000 FC000000 FD000000 FF800A00

80A11800 81000300 82208200 83F00000 84FFFF00 85FF0700 86FFFF00 87260000 88049300 891F0000 8A000000 8B000000 8C030000 8D030000 8E040000 8F040000 90000000 91000000 92000000 93000000 94000000 95000000 96000000 97000000 98000000 99000000 9A000000 9B340800 9E999900 9F998000 A0800800 A21B1100 A301FF00 A4003000 A5200000 A6000000 AD000100 AEFFFF00 AF000400 B0000000 B1040300 B2072000 B3E41000 B4000000 BB980000 BC805000 BD008800 BE010800 BF000000 C1000000 C2000000 C3000000 C4000000 C6004400 C719C800 C8314300 C9000000 CA032100 CB080100 CC090100 CD010000 CE0F0F00 CF1C4100 D0000000 D100DF00 D200FF00 D3000000 D400FF00 D500FF00 D6000000 D700FF00 D800FF00 D9000000 DA00FF00 DB00FF00 DC113300 DE000000 DF012300 E0576400 E1021100 E4F70300 E5F70300 E6DF0F00 E7DD0F00 E8FF0F00 E9FF0F00 EACF0F00 EBF30E00 EC000700 ED00F000 EE000000 EF000000 F0000000 F1000000 F2000000 F3000000 F4000000 F5000000 F6000000 F7000000 F8000000 F9000000 FA000000 FB000000 FC000000 FD000000 FF800A00