Hello,

Running ADS1263 and getting everything working good in waiting/polling mode.

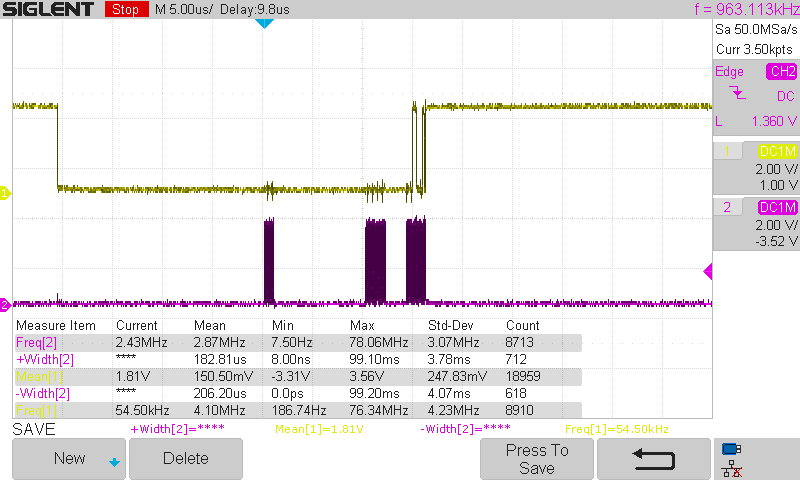

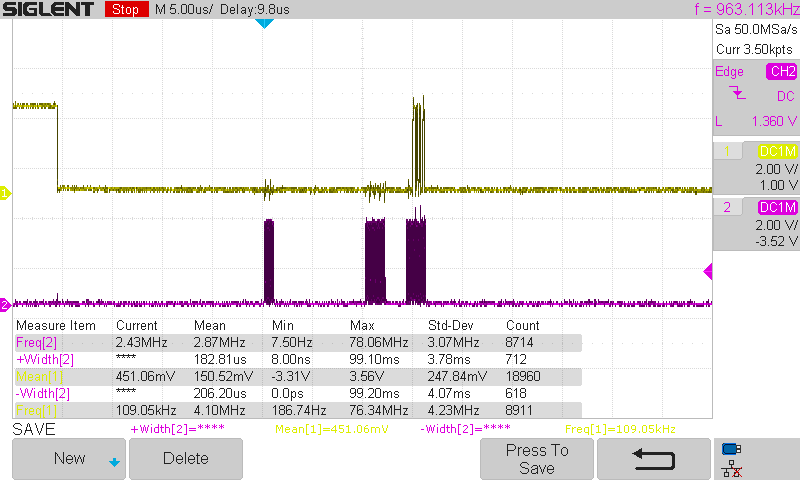

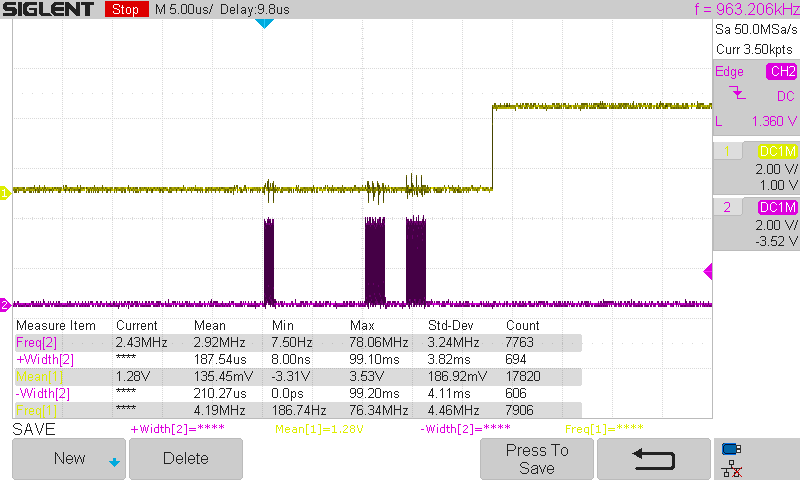

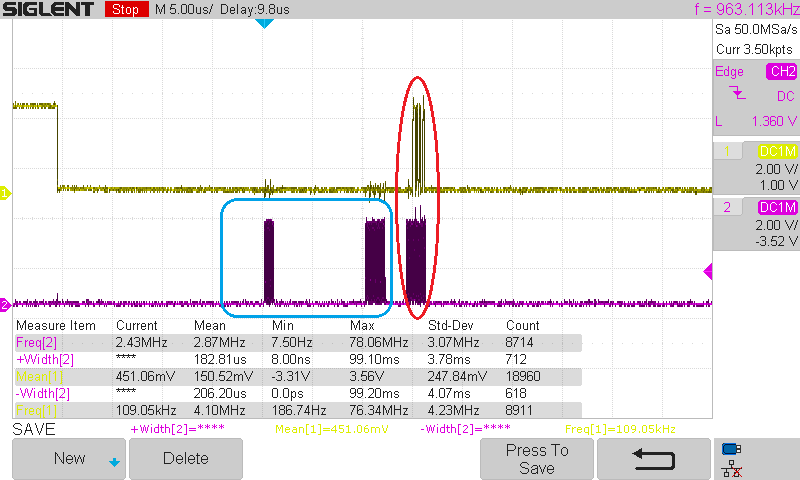

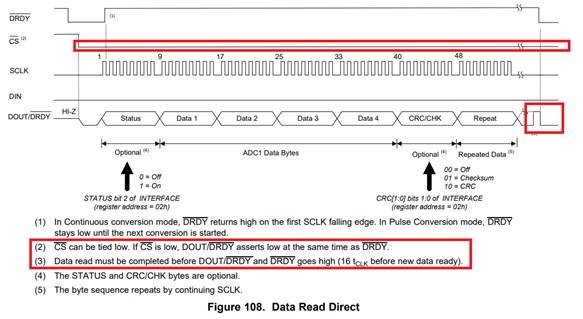

When using interrupts on DOUT/DRDY line however the line seem to keep the last data bit instead of following the dedicated DRDY line. So, setting an interrupt on the DOUT/DRDY line and getting CS low half times (when last bit was low) it fires immediately instead of waiting for the new data ready.

The dedicated DRDY line works perfectly fine, however by design I was supposed to rely on the DOUT/DRDY and MCU does not have access to dedicated DRDY line.

Am I missing something?...

Thank you for your help,

A.