Sorry, the ADS1158EVM-PDK does not work in my environment, so I will change the approach.

I Check the operation only with the ADS1158EVM.

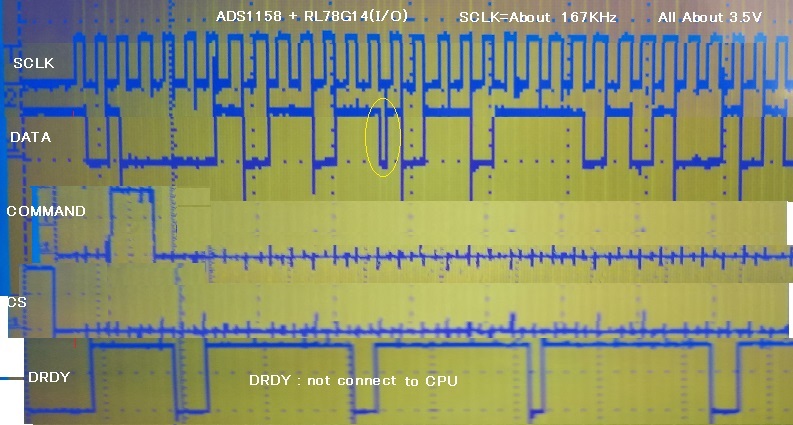

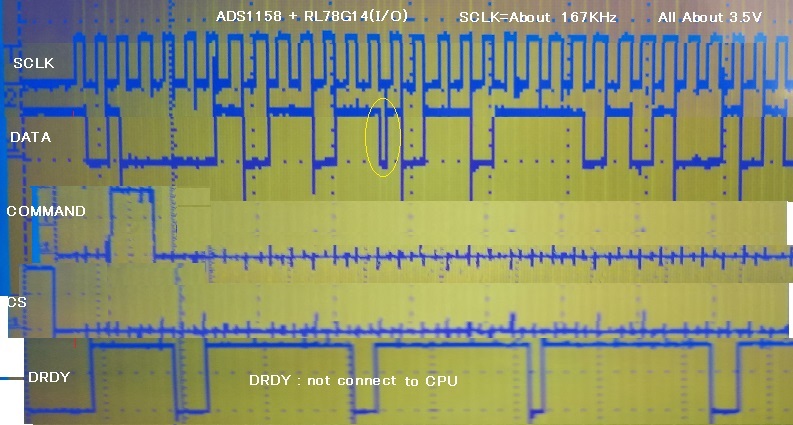

With ADS1158EVM + CPU (RenesasRL78G14), SPI emuration with Didital I / O.

In my program I wrote 0x02 at address 000 and 0x01 at 001. I confirmed the reading.

I could read 2 and 1.

Other registers are defaults.

I want to read all 16 single-ended channels.

・Send 00110000 command.

-To read status and data, send 24 clocks for required 16CH and read.

The CHID in the status doesn't seem normal. (CH0 = does not become xxx01000)

(Maybe I just don't understand the English manual)

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.