Hi, I am evaluating the DAC38RF80EVM and found some issues while it is connected to the TSW14J56 revD Board.

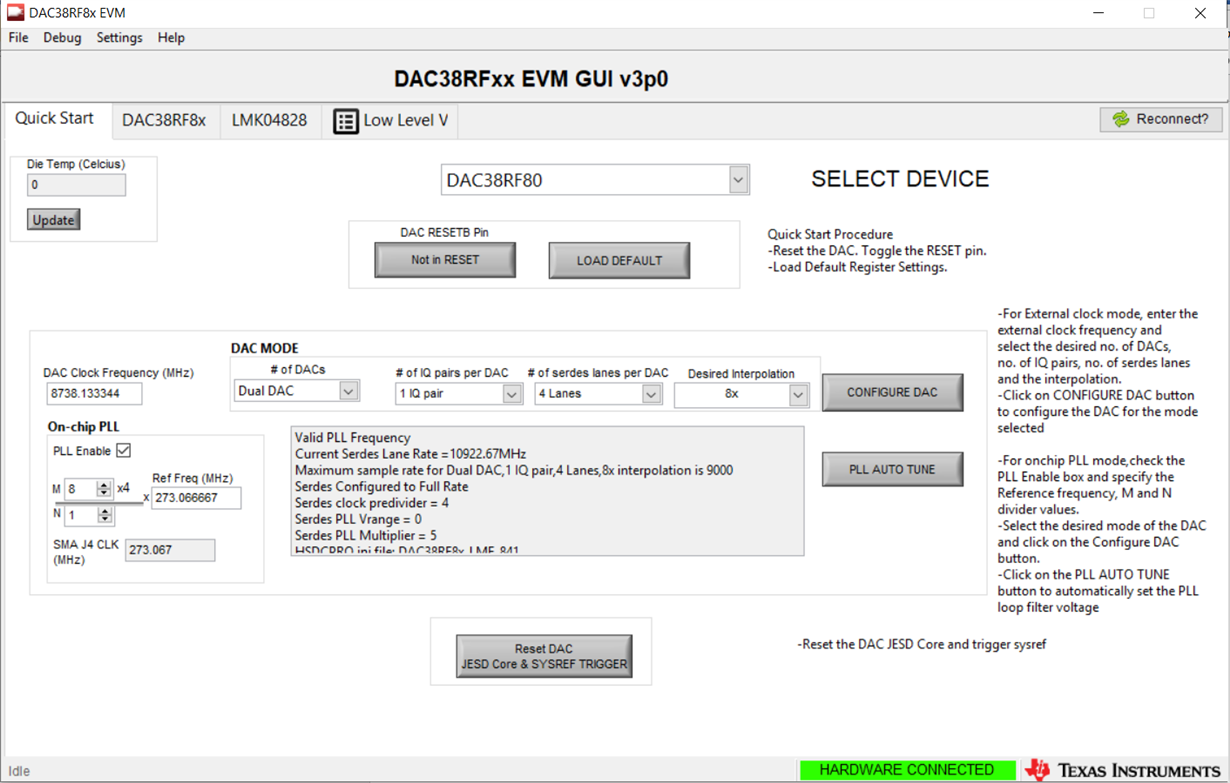

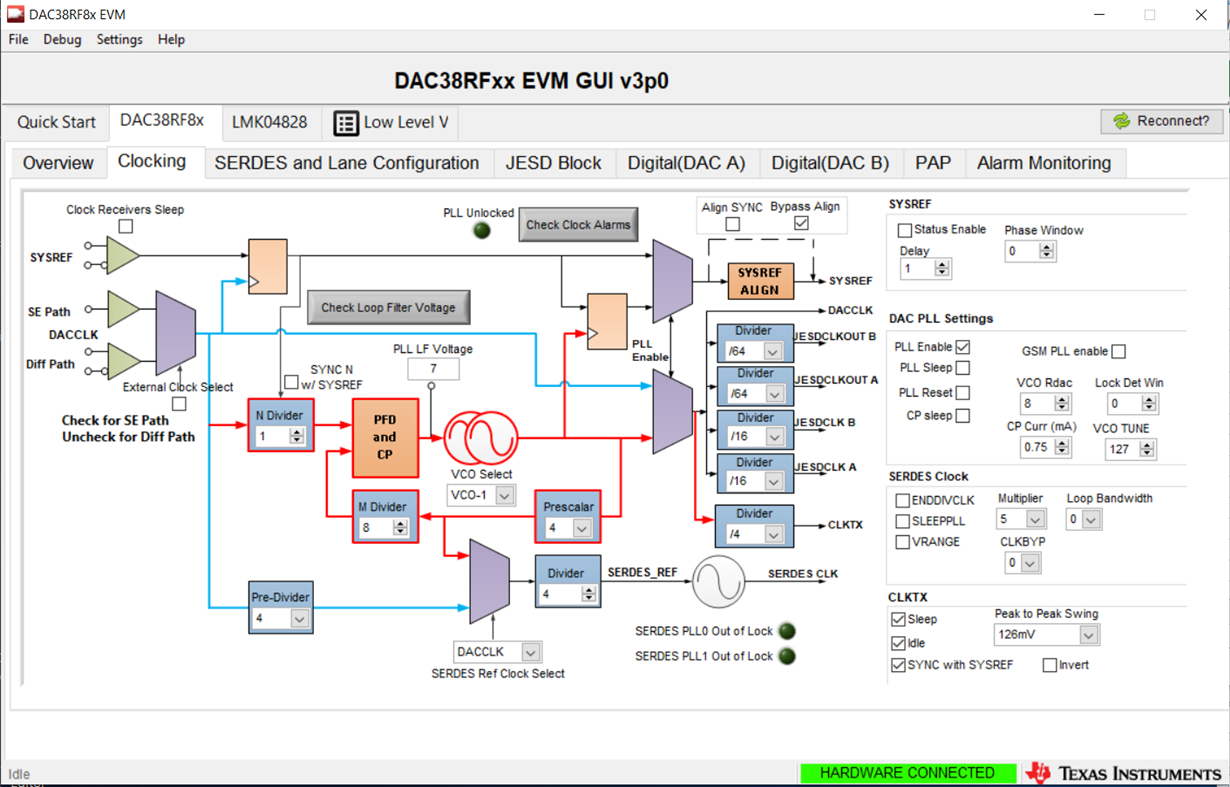

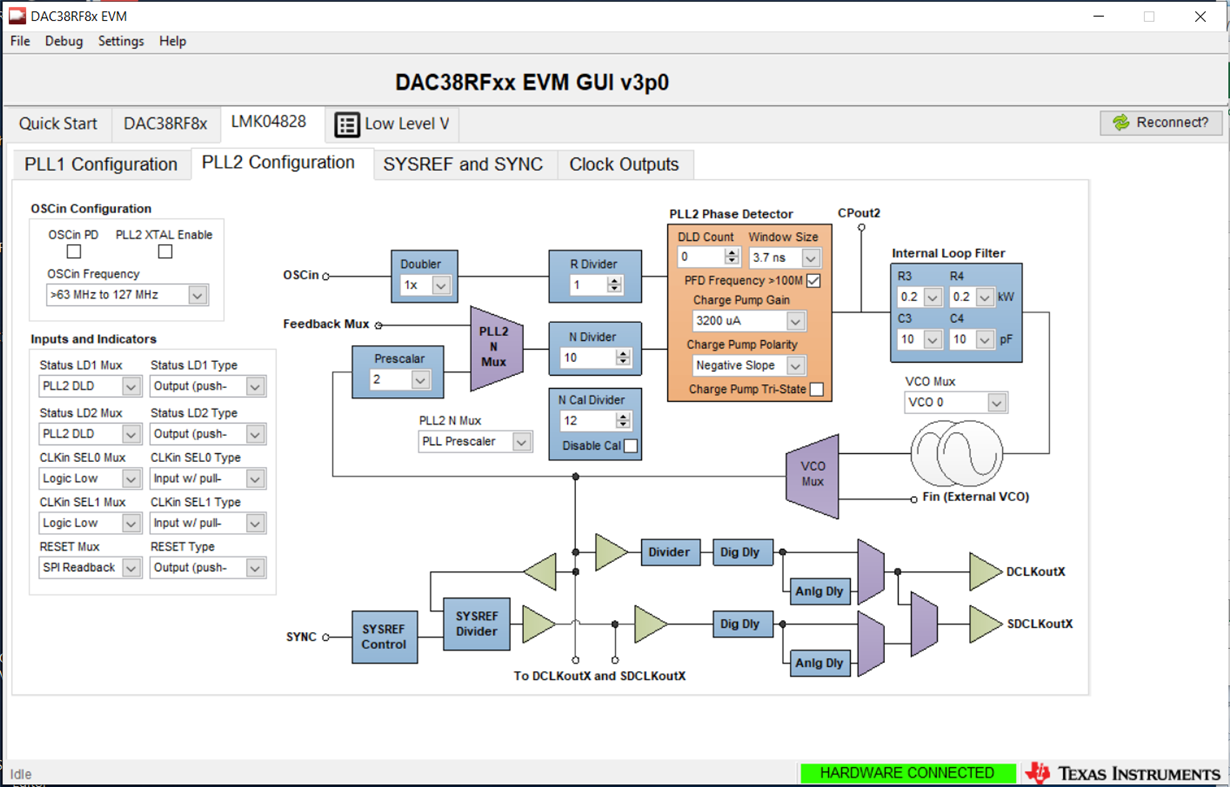

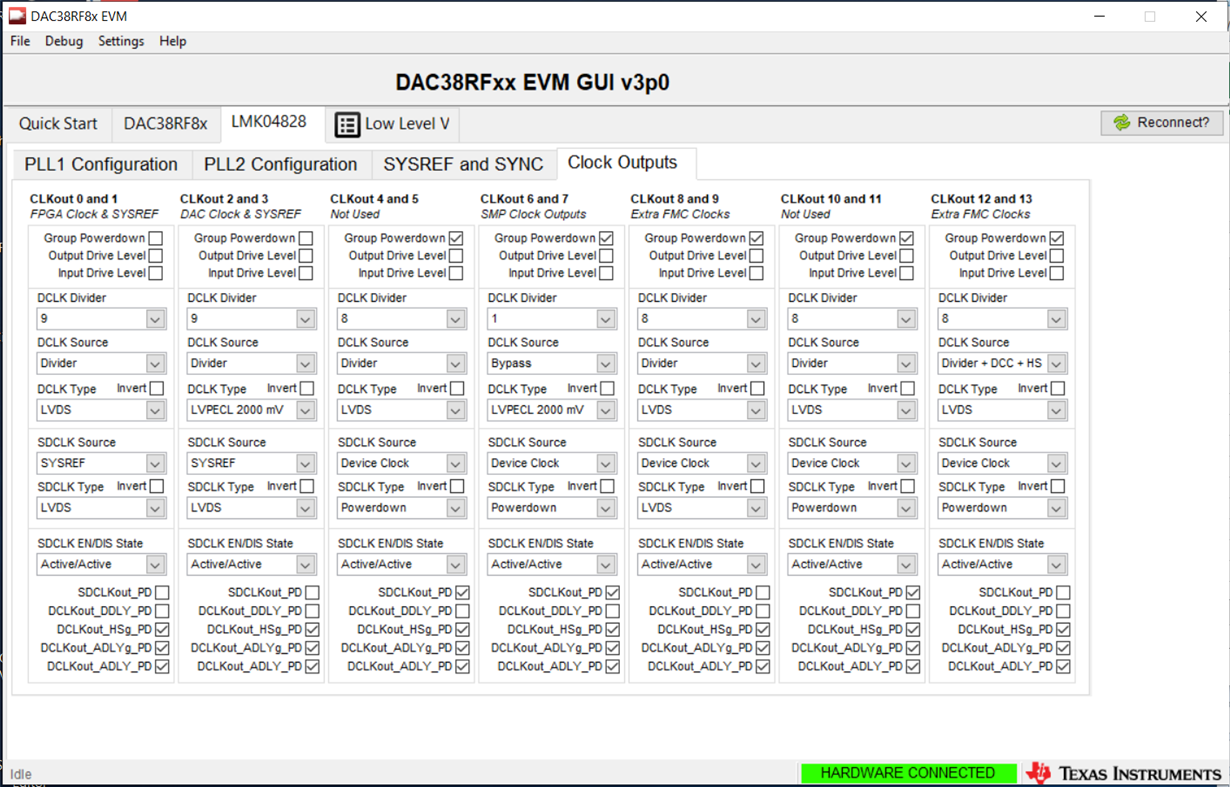

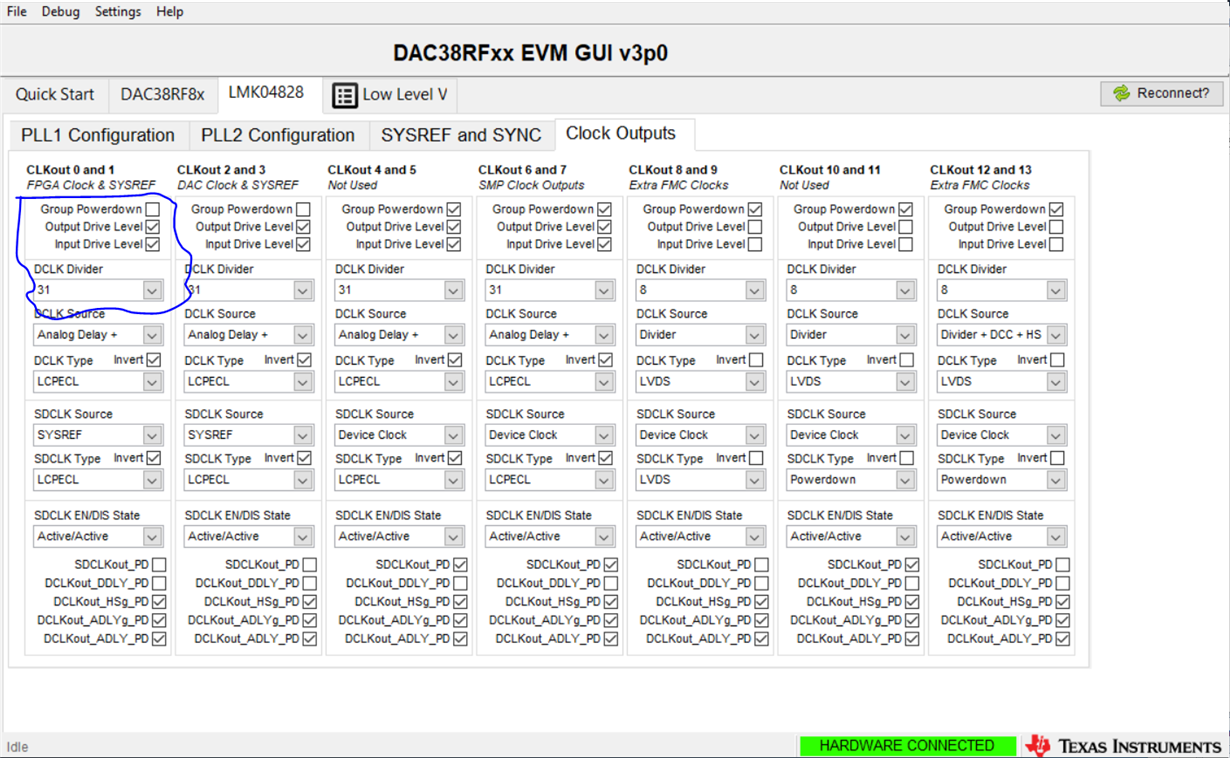

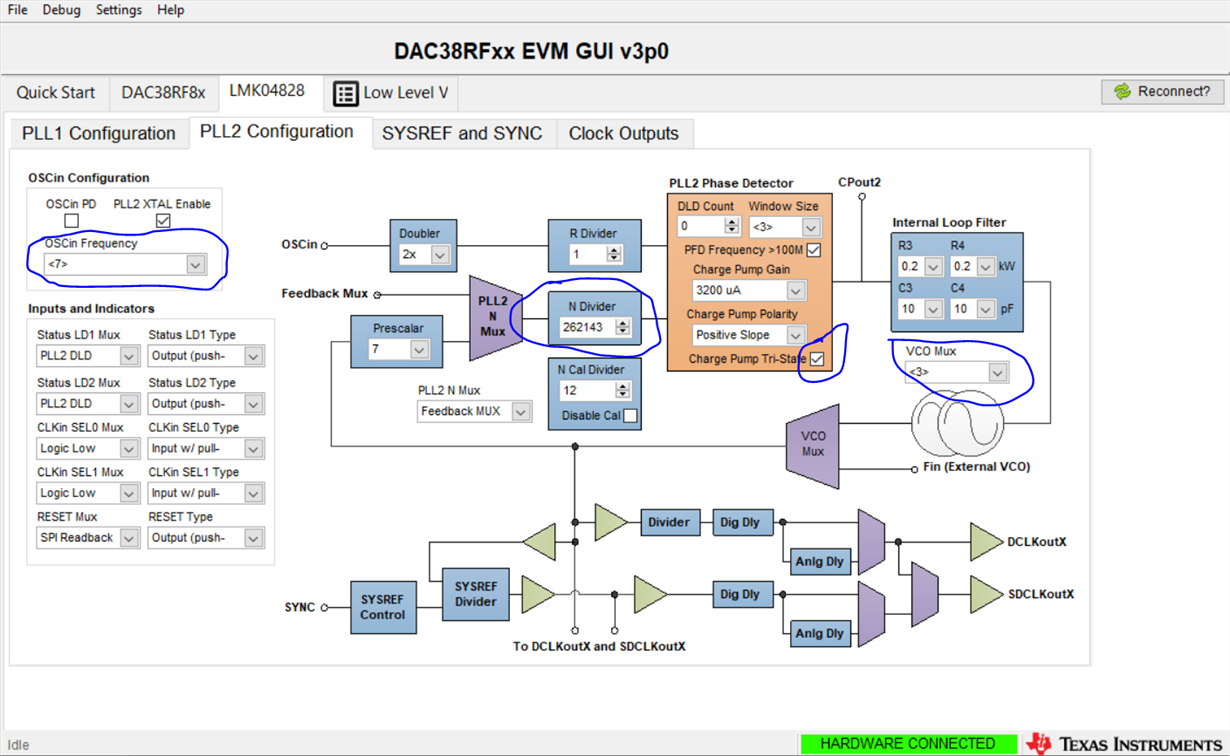

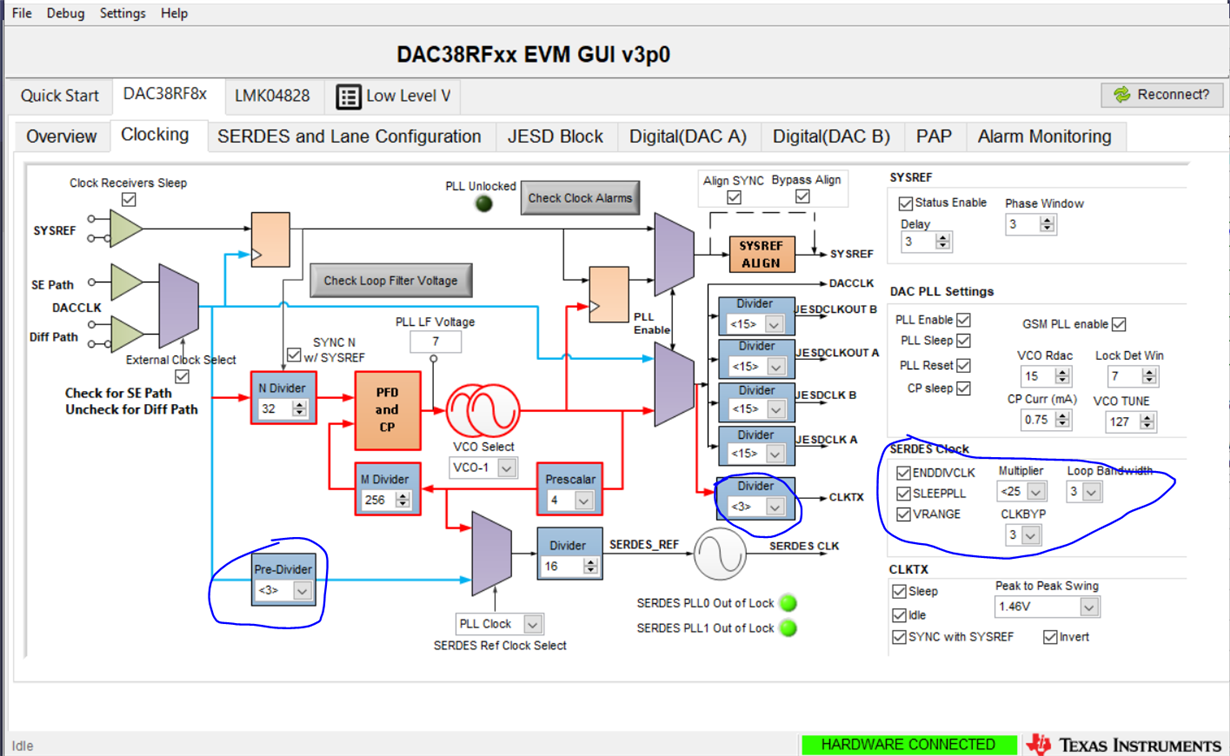

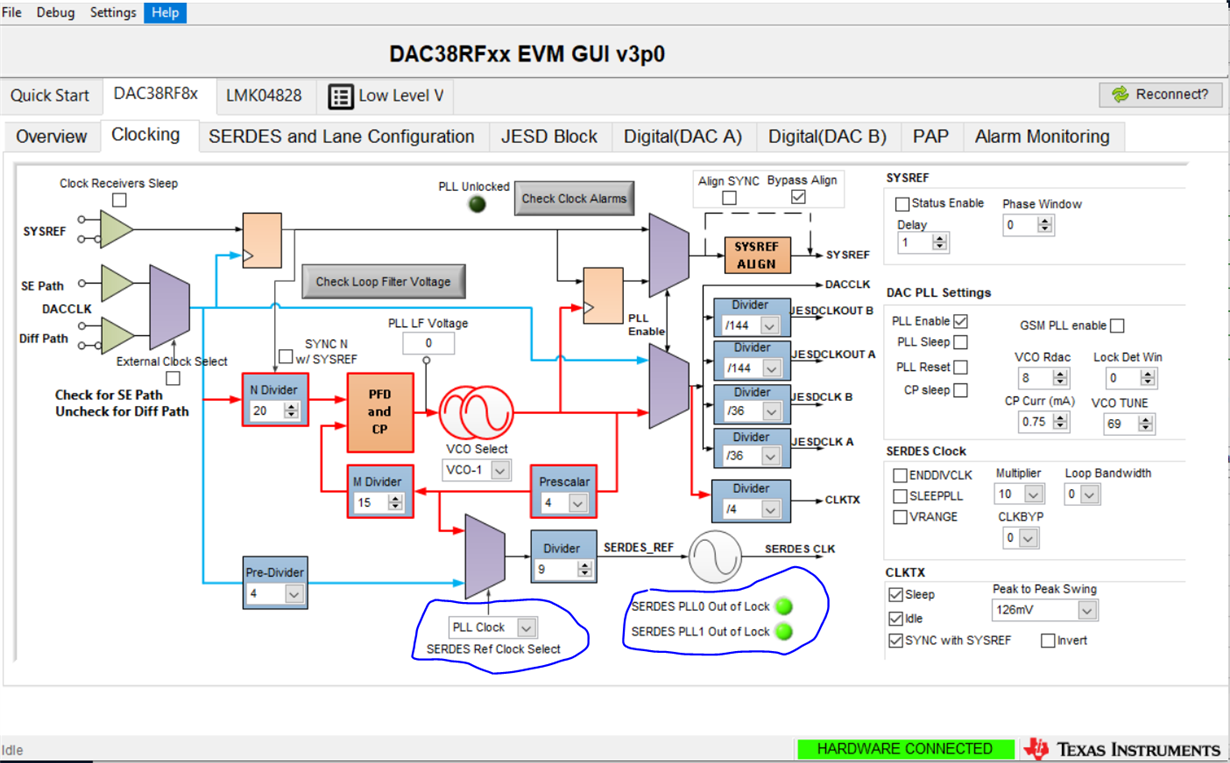

My current configuration is: using the on-board 122.88MHz oscillator as the reference into the LMK, then LMK output serving as DACCLK and FPGA CLK. To get this working, I DNI C333 and C334 and install C2 and C3 based on the schematic. With this modification, I can see the LMK clk output into the DAC, and have the DAC PLL locked when FPGA board is turned off. The GUI configuration is shown below:

Without the FPGA board, I can control the registers of the DAC and LMK through GUI just fine, and successfully get the correct DAC output using the constant data mode.

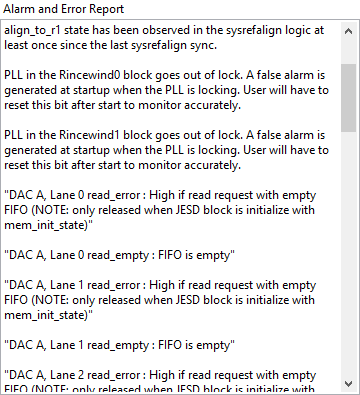

However, once I turned on the TSW14J56revD FPGA board, the DAC eval board’s registers cannot be modified through GUI. For example, I set the LMK DCLK Divider to 9, it reads back as 31. I cannot change the N Divider of LMK and CP tri-state is always on. VCO selection is not available. Ocs-in selection is not available. And I cannot set the DAC registers in the clocking tab. As a result, the DAC PLL is shown as unlocked.

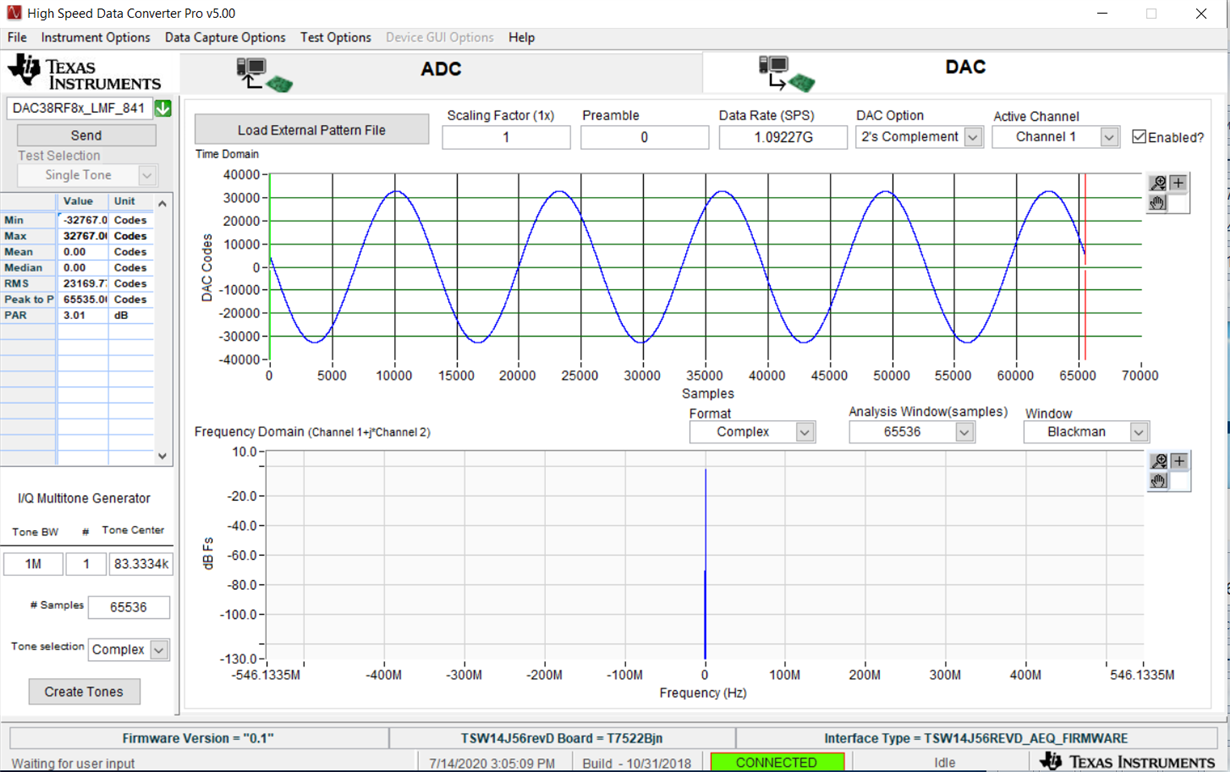

I then tried to create patterns from the FPGA board and send to DAC board:

I got this warning: JESD REF CLK needs to be 237.0665MHz.

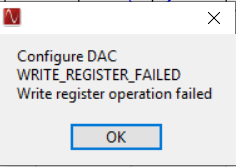

Then I got this error message: WRITE_REGISTER_FAILED

So I have the following questions:

1) Is this the correct configuration for using on-board 122.88MHz osc as LMK ref and LMK output as DACCLK and FPGA CLK.

2) Does the freq configuration make sense for LMK and DAC to get the correct DACCLK, FPGA CLK, JESD reference clk? Will I always get the 1st warning message about the JESD reference clk?

3) Why the FPGA board keeps resetting the registers? I tried two revD board and observed the same thing.

Thanks for your support.