Other Parts Discussed in Thread: LMK04826

Hi

We are having an issue with the DAC38J84.

FPGA --- Virtex 7

Clock Generator --- LMK04826

DAC --- DAC38J84

In the DAC34J84, there are some Error / Alarm indications

a. 8b/10b Disparity error

b. 8b/10b Not in table code error

c. Code Synchronization error

d. Elastic Buffer Overflow error

e. Link Configuration error

f. Frame Alignment error

g. Multiframe Alignment error

h. FIFO Full

i. FIFO Empty

We are configuring DAC in two modes

1. At Low Speed 312.5 MSPS Sampling rate.

2. At High Speed 2.5 GSPS Sampling rate.

Case 1 : Low Speed

SERDES Rate = 6.25 Gbps

LMK Clk Frequency to FPGA = 156.25 MHz (SERDES Rate / 40)

LMK Clk Frequency to DAC = 312.50 MHz

SYSREF Frequency = 4.8828125 MHz (FPGA Clk / 64)

Interpolation = x 1

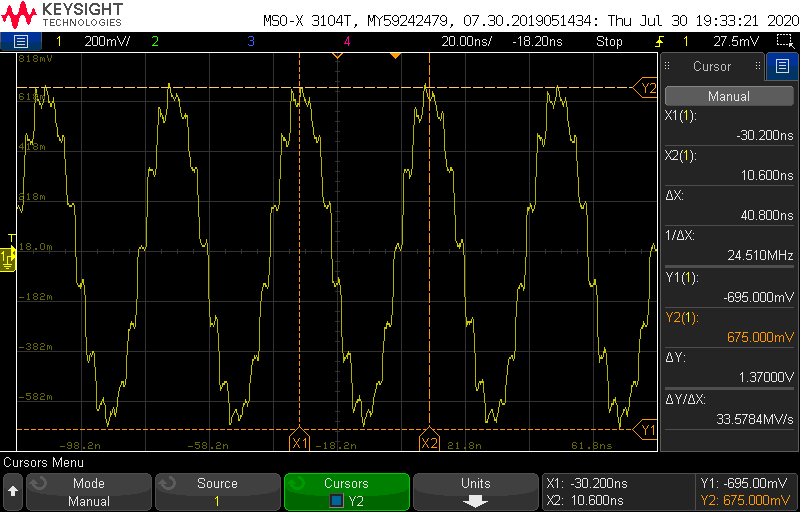

Output Data from DAC = Singletone 25 MHz

We are measuring the clock coming to FPGA and DAC. They are as per specs.

At low Speed, we are able to capture the correct data from DAC.

JESD Link up is done and there are NO ALARMS in DAC.

Case 2 : High Speed

SERDES Rate = 6.25 Gbps

LMK Clk Frequency to FPGA = 156.25 MHz (SERDES Rate / 40)

LMK Clk Frequency to DAC = 2.5 GHz

SYSREF Frequency = 4.8828125 MHz (FPGA Clk / 64)

Interpolation = x 8

Output Data from DAC = Singletone 25 MHz

We are measuring the clock coming to FPGA and DAC. They are as per specs.

At High Speed, we are unable to capture the correct data from DAC.

JESD Sync Signal is continuously toggling and there are ALARMS in DAC.

We are getting the following ALARM / Error indications at High Speed

a. 8b/10b Disparity error

b. 8b/10b Not in table code error

c. Code Synchronization error

d. Elastic Buffer Overflow error

e. Frame Alignment error

f. Multiframe Alignment error

g. FIFO Full

h. FIFO Empty

These errors indicate that there is problem with JESD Link up at high speed.

It would be helpful if you guide us to resolve this issue

Please Find Attachments :

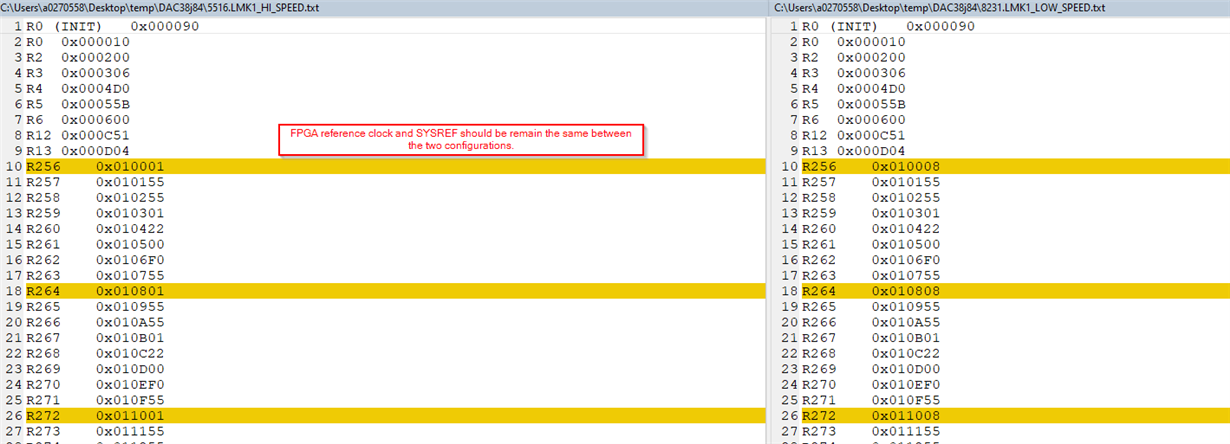

1. LMK Configuration files at Low and High speeds

2. DAC Configuration files at Low and High Speeds

3. DAC Outputs at Low speed

R0 (INIT) 0x000090 R0 0x000010 R2 0x000200 R3 0x000306 R4 0x0004D0 R5 0x00055B R6 0x000600 R12 0x000C51 R13 0x000D04 R256 0x010008 R257 0x010155 R258 0x010255 R259 0x010301 R260 0x010422 R261 0x010500 R262 0x0106F0 R263 0x010755 R264 0x010808 R265 0x010955 R266 0x010A55 R267 0x010B01 R268 0x010C22 R269 0x010D00 R270 0x010EF0 R271 0x010F55 R272 0x011008 R273 0x011155 R274 0x011255 R275 0x011301 R276 0x011422 R277 0x011500 R278 0x0116F0 R279 0x011755 R280 0x011810 R281 0x011955 R282 0x011A55 R283 0x011B01 R284 0x011C22 R285 0x011D00 R286 0x011EF0 R287 0x011F11 R288 0x012010 R289 0x012155 R290 0x012255 R291 0x012301 R292 0x012422 R293 0x012500 R294 0x0126F0 R295 0x012711 R296 0x012810 R297 0x012955 R298 0x012A55 R299 0x012B01 R300 0x012C22 R301 0x012D00 R302 0x012EF0 R303 0x012F11 R304 0x013019 R305 0x013155 R306 0x013255 R307 0x013301 R308 0x013402 R309 0x013500 R310 0x0136F1 R311 0x013701 R312 0x013820 R313 0x013903 R314 0x013A02 R315 0x013B00 R316 0x013C00 R317 0x013D08 R318 0x013E03 R319 0x013F00 R320 0x01408B R321 0x014100 R322 0x014200 R323 0x014311 R324 0x0144FF R325 0x01457F R326 0x014618 R327 0x01471A R328 0x014802 R329 0x014942 R330 0x014A02 R331 0x014B16 R332 0x014C00 R333 0x014D00 R334 0x014EC0 R335 0x014F7F R336 0x015003 R337 0x015102 R338 0x015200 R339 0x015300 R340 0x015478 R341 0x015500 R342 0x015678 R343 0x015700 R344 0x015896 R345 0x015900 R346 0x015A78 R347 0x015BD4 R348 0x015C20 R349 0x015D00 R350 0x015E00 R351 0x015F0B R352 0x016000 R353 0x016101 R354 0x0162A4 R355 0x016300 R356 0x016400 R357 0x01650A R369 0x0171AA R370 0x017202 R380 0x017C18 R381 0x017D77 R358 0x016600 R359 0x016700 R360 0x016805 R361 0x016959 R362 0x016A20 R363 0x016B00 R364 0x016C00 R365 0x016D00 R366 0x016E13 R371 0x017300 R8189 0x1FFD00 R8190 0x1FFE00 R8191 0x1FFF53

R0 (INIT) 0x000090 R0 0x000010 R2 0x000200 R3 0x000306 R4 0x0004D0 R5 0x00055B R6 0x000600 R12 0x000C51 R13 0x000D04 R256 0x010001 R257 0x010155 R258 0x010255 R259 0x010301 R260 0x010422 R261 0x010500 R262 0x0106F0 R263 0x010755 R264 0x010801 R265 0x010955 R266 0x010A55 R267 0x010B01 R268 0x010C22 R269 0x010D00 R270 0x010EF0 R271 0x010F55 R272 0x011001 R273 0x011155 R274 0x011255 R275 0x011301 R276 0x011422 R277 0x011500 R278 0x0116F0 R279 0x011755 R280 0x011810 R281 0x011955 R282 0x011A55 R283 0x011B01 R284 0x011C22 R285 0x011D00 R286 0x011EF0 R287 0x011F11 R288 0x012010 R289 0x012155 R290 0x012255 R291 0x012301 R292 0x012422 R293 0x012500 R294 0x0126F0 R295 0x012711 R296 0x012810 R297 0x012955 R298 0x012A55 R299 0x012B01 R300 0x012C22 R301 0x012D00 R302 0x012EF0 R303 0x012F11 R304 0x013019 R305 0x013155 R306 0x013255 R307 0x013301 R308 0x013402 R309 0x013500 R310 0x0136F1 R311 0x013701 R312 0x013820 R313 0x013903 R314 0x013A02 R315 0x013B00 R316 0x013C00 R317 0x013D08 R318 0x013E03 R319 0x013F00 R320 0x01408B R321 0x014100 R322 0x014200 R323 0x014311 R324 0x0144FF R325 0x01457F R326 0x014618 R327 0x01471A R328 0x014802 R329 0x014942 R330 0x014A02 R331 0x014B16 R332 0x014C00 R333 0x014D00 R334 0x014EC0 R335 0x014F7F R336 0x015003 R337 0x015102 R338 0x015200 R339 0x015300 R340 0x015478 R341 0x015500 R342 0x015678 R343 0x015700 R344 0x015896 R345 0x015900 R346 0x015A78 R347 0x015BD4 R348 0x015C20 R349 0x015D00 R350 0x015E00 R351 0x015F0B R352 0x016000 R353 0x016101 R354 0x0162A4 R355 0x016300 R356 0x016400 R357 0x01650A R369 0x0171AA R370 0x017202 R380 0x017C18 R381 0x017D77 R358 0x016600 R359 0x016700 R360 0x016805 R361 0x016959 R362 0x016A20 R363 0x016B00 R364 0x016C00 R365 0x016D00 R366 0x016E13 R371 0x017300 R8189 0x1FFD00 R8190 0x1FFE00 R8191 0x1FFF53

# DAC configuration # 442 with x1 Interpolation Low Speed dac_address: 0x0 dac_data : 0x258 dac_address: 0x1 dac_data : 0x3 dac_address: 0x2 dac_data : 0x2082 dac_address: 0x3 dac_data : 0xA300 dac_address: 0x4 dac_data : 0xF0F0 dac_address: 0x5 dac_data : 0xFF07 dac_address: 0x6 dac_data : 0xFFFF dac_address: 0x7 dac_data : 0x3100 dac_address: 0x8 dac_data : 0x0 dac_address: 0x9 dac_data : 0x0 dac_address: 0xA dac_data : 0x0 dac_address: 0xB dac_data : 0x0 dac_address: 0xC dac_data : 0x400 dac_address: 0xD dac_data : 0x400 dac_address: 0xE dac_data : 0x400 dac_address: 0xF dac_data : 0x400 dac_address: 0x10 dac_data : 0x0 dac_address: 0x11 dac_data : 0x0 dac_address: 0x12 dac_data : 0x0 dac_address: 0x13 dac_data : 0x0 dac_address: 0x14 dac_data : 0x0 dac_address: 0x15 dac_data : 0x0 dac_address: 0x16 dac_data : 0x0 dac_address: 0x17 dac_data : 0x0 dac_address: 0x18 dac_data : 0x0 dac_address: 0x19 dac_data : 0x0 dac_address: 0x1A dac_data : 0x20 dac_address: 0x1B dac_data : 0x0 dac_address: 0x1E dac_data : 0x9999 dac_address: 0x1F dac_data : 0x9980 dac_address: 0x20 dac_data : 0x8008 dac_address: 0x22 dac_data : 0x1B1B dac_address: 0x23 dac_data : 0x1FF dac_address: 0x24 dac_data : 0x20 dac_address: 0x25 dac_data : 0x4000 dac_address: 0x26 dac_data : 0x0 dac_address: 0x2D dac_data : 0x1 dac_address: 0x2E dac_data : 0xFFFF dac_address: 0x2F dac_data : 0x4 dac_address: 0x30 dac_data : 0x0 dac_address: 0x31 dac_data : 0x1000 dac_address: 0x32 dac_data : 0x0 dac_address: 0x33 dac_data : 0x0 dac_address: 0x34 dac_data : 0x0 dac_address: 0x3B dac_data : 0x1800 dac_address: 0x3C dac_data : 0x228 dac_address: 0x3D dac_data : 0x88 dac_address: 0x3E dac_data : 0x108 dac_address: 0x3F dac_data : 0x0 dac_address: 0x46 dac_data : 0x1882 dac_address: 0x47 dac_data : 0x1C8 dac_address: 0x48 dac_data : 0x3143 dac_address: 0x49 dac_data : 0x0 dac_address: 0x4A dac_data : 0xF1E dac_address: 0x4B dac_data : 0x801 dac_address: 0x4C dac_data : 0x903 dac_address: 0x4D dac_data : 0x300 dac_address: 0x4E dac_data : 0xF0F dac_address: 0x4F dac_data : 0x1C61 dac_address: 0x50 dac_data : 0x0 dac_address: 0x51 dac_data : 0xDC dac_address: 0x52 dac_data : 0xFF dac_address: 0x53 dac_data : 0x0 dac_address: 0x54 dac_data : 0xFC dac_address: 0x55 dac_data : 0xFF dac_address: 0x56 dac_data : 0x0 dac_address: 0x57 dac_data : 0xFF dac_address: 0x58 dac_data : 0xFF dac_address: 0x59 dac_data : 0x0 dac_address: 0x5A dac_data : 0xFF dac_address: 0x5B dac_data : 0xFF dac_address: 0x5C dac_data : 0x1133 dac_address: 0x5E dac_data : 0x0 dac_address: 0x5F dac_data : 0x3210 dac_address: 0x60 dac_data : 0x5764 dac_address: 0x61 dac_data : 0x211 dac_address: 0x64 dac_data : 0x1 dac_address: 0x65 dac_data : 0x1 dac_address: 0x66 dac_data : 0x1 dac_address: 0x67 dac_data : 0x1 dac_address: 0x68 dac_data : 0x7709 dac_address: 0x69 dac_data : 0x0 dac_address: 0x6A dac_data : 0x0 dac_address: 0x6B dac_data : 0xBD07 dac_address: 0x6C dac_data : 0x7 dac_address: 0x6D dac_data : 0x90 dac_address: 0x6E dac_data : 0x0 dac_address: 0x6F dac_data : 0x0 dac_address: 0x70 dac_data : 0x0 dac_address: 0x71 dac_data : 0x0 dac_address: 0x72 dac_data : 0x0 dac_address: 0x73 dac_data : 0x0 dac_address: 0x74 dac_data : 0x0 dac_address: 0x75 dac_data : 0x0 dac_address: 0x76 dac_data : 0x0 dac_address: 0x77 dac_data : 0x0 dac_address: 0x78 dac_data : 0x0 dac_address: 0x79 dac_data : 0x0 dac_address: 0x7A dac_data : 0x0 dac_address: 0x7B dac_data : 0x0 dac_address: 0x7C dac_data : 0x0 dac_address: 0x7D dac_data : 0x0 dac_address: 0x3B dac_data : 0x0 dac_address: 0x25 dac_data : 0x0 dac_address: 0x3C dac_data : 0x250 dac_address: 0x3C dac_data : 0x50 dac_address: 0x3E dac_data : 0x128 dac_address: 0x4C dac_data : 0x903 dac_address: 0x4D dac_data : 0x300 dac_address: 0x4B dac_data : 0x801 dac_address: 0x4D dac_data : 0x300 dac_address: 0x4E dac_data : 0xF0F dac_address: 0x0 dac_data : 0x18

# DAC configuration # 442 with x8 Interpolation High Speed dac_address : 0x0 dac_data : 0x418 dac_address : 0x1 dac_data : 0x3 dac_address : 0x2 dac_data : 0x2082 dac_address : 0x3 dac_data : 0xA300 dac_address : 0x4 dac_data : 0xF0F0 dac_address : 0x5 dac_data : 0xFF07 dac_address : 0x6 dac_data : 0xFFFF dac_address : 0x7 dac_data : 0x3100 dac_address : 0x8 dac_data : 0x0 dac_address : 0x9 dac_data : 0x0 dac_address : 0xA dac_data : 0x0 dac_address : 0xB dac_data : 0x0 dac_address : 0xC dac_data : 0x400 dac_address : 0xD dac_data : 0x400 dac_address : 0xE dac_data : 0x400 dac_address : 0xF dac_data : 0x400 dac_address : 0x10 dac_data : 0x0 dac_address : 0x11 dac_data : 0x0 dac_address : 0x12 dac_data : 0x0 dac_address : 0x13 dac_data : 0x0 dac_address : 0x14 dac_data : 0x0 dac_address : 0x15 dac_data : 0x0 dac_address : 0x16 dac_data : 0x0 dac_address : 0x17 dac_data : 0x0 dac_address : 0x18 dac_data : 0x0 dac_address : 0x19 dac_data : 0x0 dac_address : 0x1A dac_data : 0x20 dac_address : 0x1B dac_data : 0x0 dac_address : 0x1E dac_data : 0x9999 dac_address : 0x1F dac_data : 0x9980 dac_address : 0x20 dac_data : 0x8008 dac_address : 0x22 dac_data : 0x1B1B dac_address : 0x23 dac_data : 0x1FF dac_address : 0x24 dac_data : 0x20 dac_address : 0x25 dac_data : 0x4000 dac_address : 0x26 dac_data : 0x0 dac_address : 0x2D dac_data : 0x1 dac_address : 0x2E dac_data : 0xFFFF dac_address : 0x2F dac_data : 0x4 dac_address : 0x30 dac_data : 0x0 dac_address : 0x31 dac_data : 0x1000 dac_address : 0x32 dac_data : 0x0 dac_address : 0x33 dac_data : 0x0 dac_address : 0x34 dac_data : 0x0 dac_address : 0x3B dac_data : 0x1800 dac_address : 0x3C dac_data : 0x228 dac_address : 0x3D dac_data : 0x88 dac_address : 0x3E dac_data : 0x108 dac_address : 0x3F dac_data : 0x0 dac_address : 0x46 dac_data : 0x1882 dac_address : 0x47 dac_data : 0x1C8 dac_address : 0x48 dac_data : 0x3143 dac_address : 0x49 dac_data : 0x0 dac_address : 0x4A dac_data : 0xF1E dac_address : 0x4B dac_data : 0x801 dac_address : 0x4C dac_data : 0x903 dac_address : 0x4D dac_data : 0x300 dac_address : 0x4E dac_data : 0xF0F dac_address : 0x4F dac_data : 0x1C61 dac_address : 0x50 dac_data : 0x0 dac_address : 0x51 dac_data : 0xDC dac_address : 0x52 dac_data : 0xFF dac_address : 0x53 dac_data : 0x0 dac_address : 0x54 dac_data : 0xFC dac_address : 0x55 dac_data : 0xFF dac_address : 0x56 dac_data : 0x0 dac_address : 0x57 dac_data : 0xFF dac_address : 0x58 dac_data : 0xFF dac_address : 0x59 dac_data : 0x0 dac_address : 0x5A dac_data : 0xFF dac_address : 0x5B dac_data : 0xFF dac_address : 0x5C dac_data : 0x1133 dac_address : 0x5E dac_data : 0x0 dac_address : 0x5F dac_data : 0x3210 dac_address : 0x60 dac_data : 0x5764 dac_address : 0x61 dac_data : 0x211 dac_address : 0x64 dac_data : 0x1 dac_address : 0x65 dac_data : 0x1 dac_address : 0x66 dac_data : 0x1 dac_address : 0x67 dac_data : 0x1 dac_address : 0x68 dac_data : 0x7709 dac_address : 0x69 dac_data : 0x0 dac_address : 0x6A dac_data : 0x0 dac_address : 0x6B dac_data : 0xBD07 dac_address : 0x6C dac_data : 0x7 dac_address : 0x6D dac_data : 0x90 dac_address : 0x6E dac_data : 0x0 dac_address : 0x6F dac_data : 0x0 dac_address : 0x70 dac_data : 0x0 dac_address : 0x71 dac_data : 0x0 dac_address : 0x72 dac_data : 0x0 dac_address : 0x73 dac_data : 0x0 dac_address : 0x74 dac_data : 0x0 dac_address : 0x75 dac_data : 0x0 dac_address : 0x76 dac_data : 0x0 dac_address : 0x77 dac_data : 0x0 dac_address : 0x78 dac_data : 0x0 dac_address : 0x79 dac_data : 0x0 dac_address : 0x7A dac_data : 0x0 dac_address : 0x7B dac_data : 0x0 dac_address : 0x7C dac_data : 0x0 dac_address : 0x7D dac_data : 0x0 dac_address : 0x3B dac_data : 0x1800 dac_address : 0x25 dac_data : 0x6000 dac_address : 0x3C dac_data : 0x228 dac_address : 0x3C dac_data : 0x28 dac_address : 0x3E dac_data : 0x128 dac_address : 0x4C dac_data : 0x903 dac_address : 0x4D dac_data : 0x300 dac_address : 0x4B dac_data : 0x801 dac_address : 0x4D dac_data : 0x300 dac_address : 0x4E dac_data : 0xF0F

Thank You