I'm using Arria 10 example design provided by TI on customer board.

The example is has Signal Tap monitor JESD signals, in which rx_dataout (240bit) from transport layer is also there.

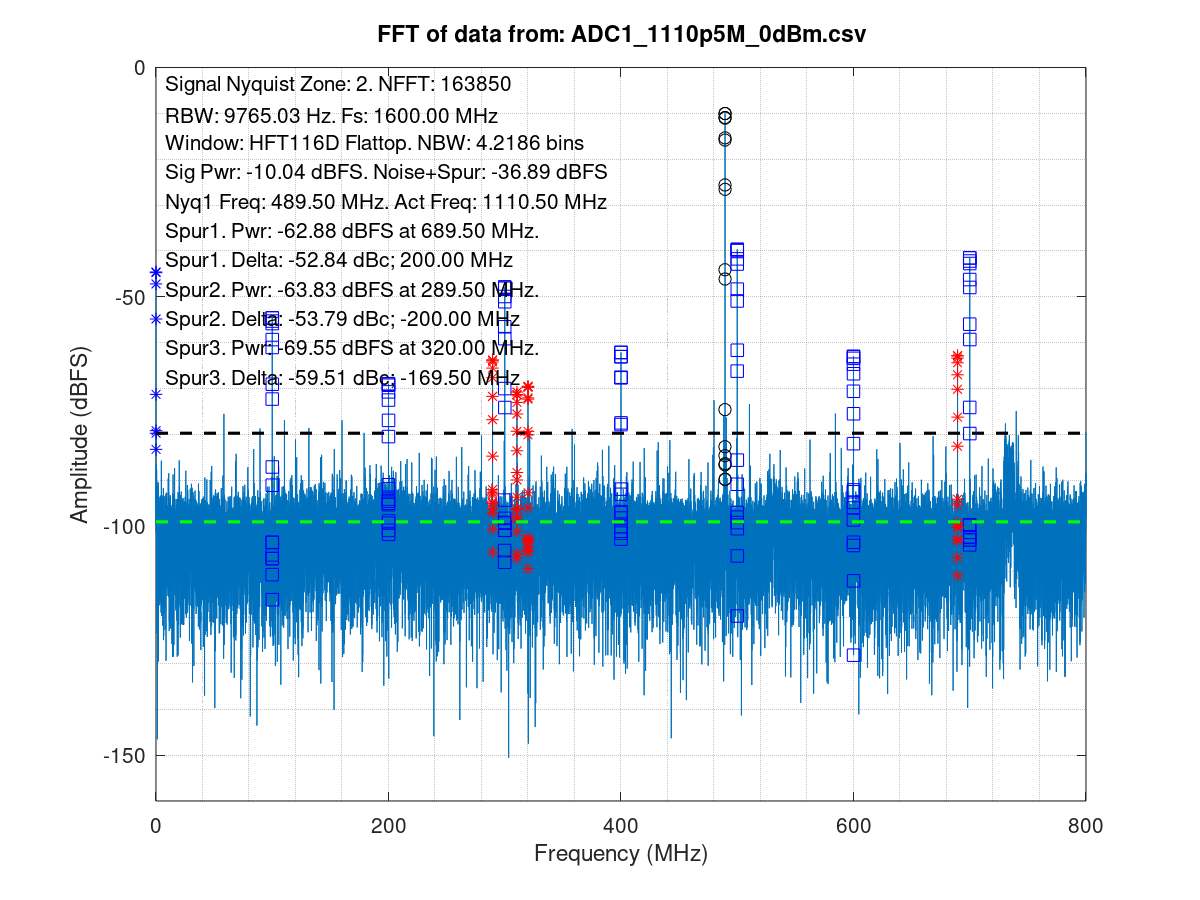

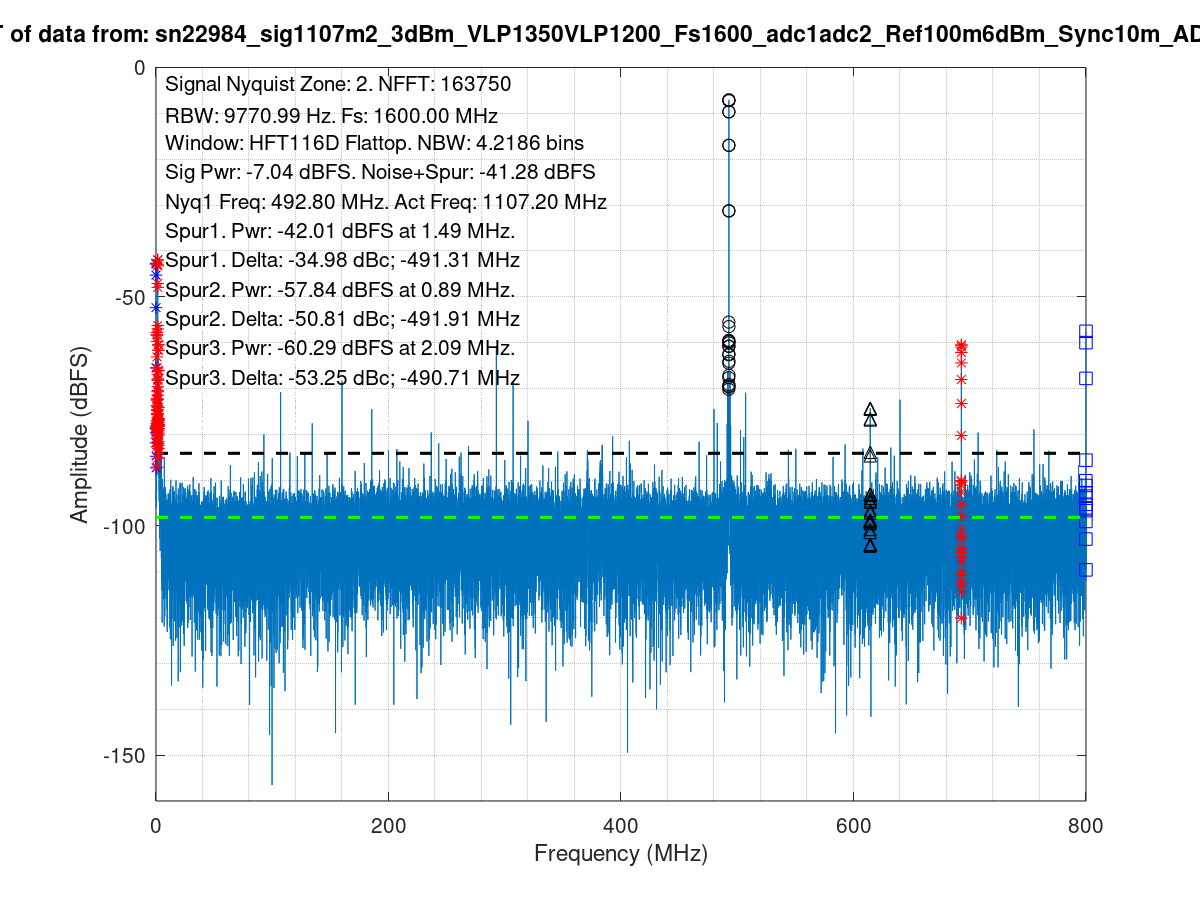

I have changed sample clock to 1.6GHz with SYSREF at 2.5MHz and the lane rate is 6.4Gbps.

I use Signal Tap to capture and monitor the data from ADC from rx_dataout by grouping it to ADC1 and ADC2 accordingly as JMODE2. Which is 120bit each.

Everything look good when using ramp (Reg205 = 0x4) and transport layer short test pattern (Reg205 = 0x5). Transport layer test pattern well aligned to rx_somfout on both ADC1 and ADC2.

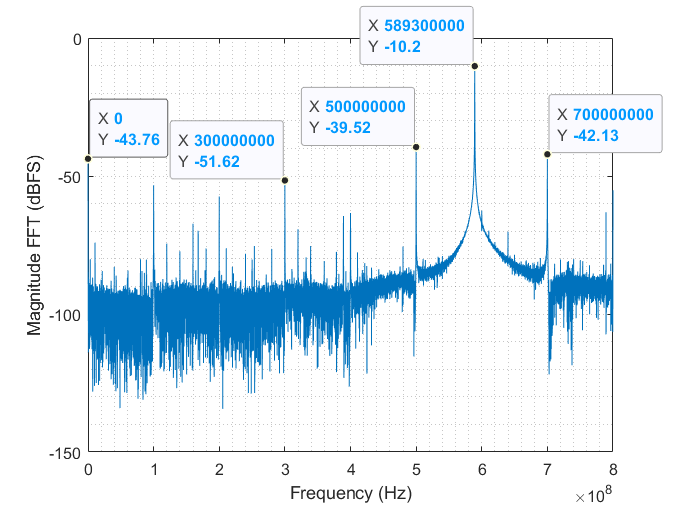

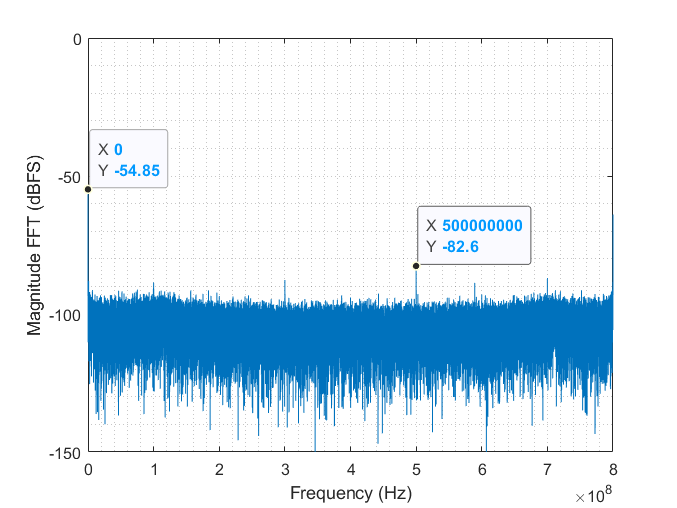

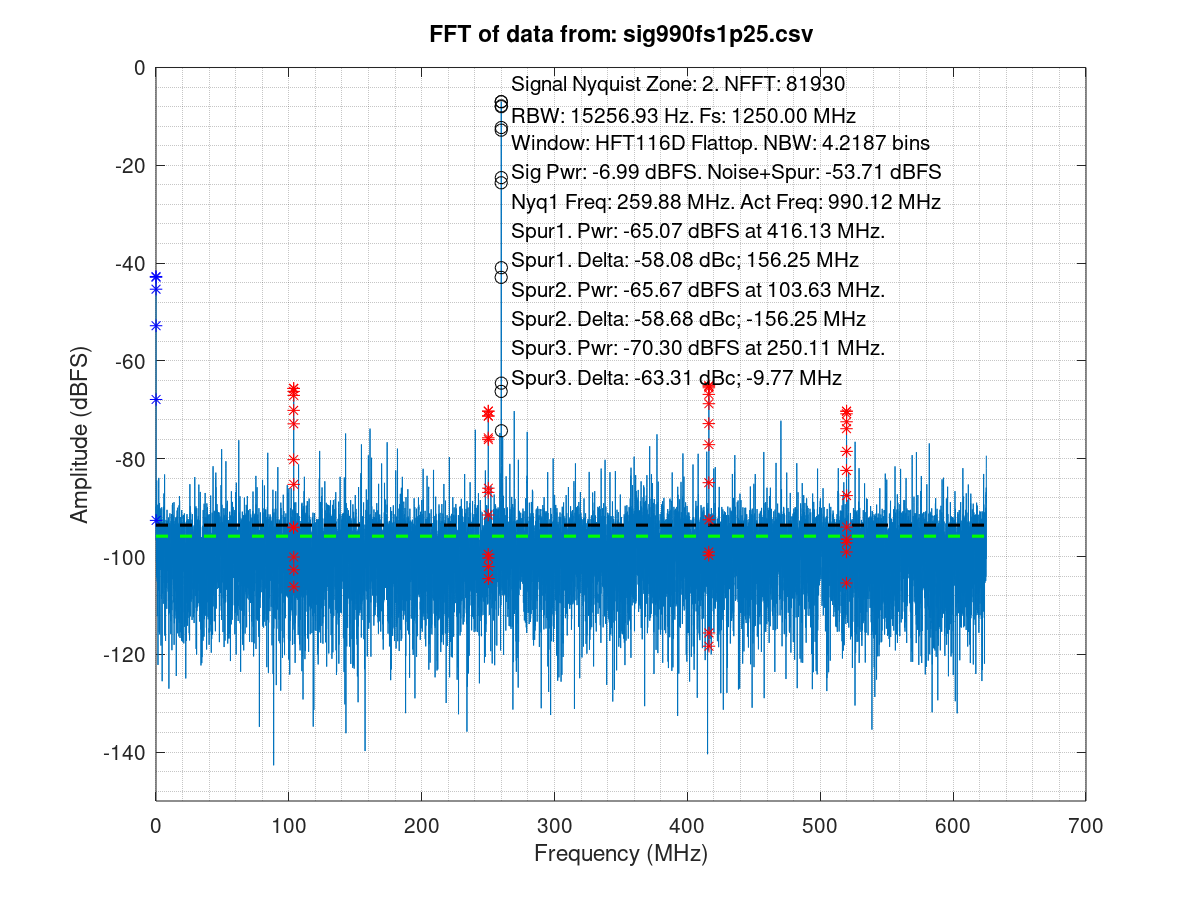

Something interesting in normal mode, for example, ADC1 has signal input of 550MHz or 900MHz or 1270MHz or so,

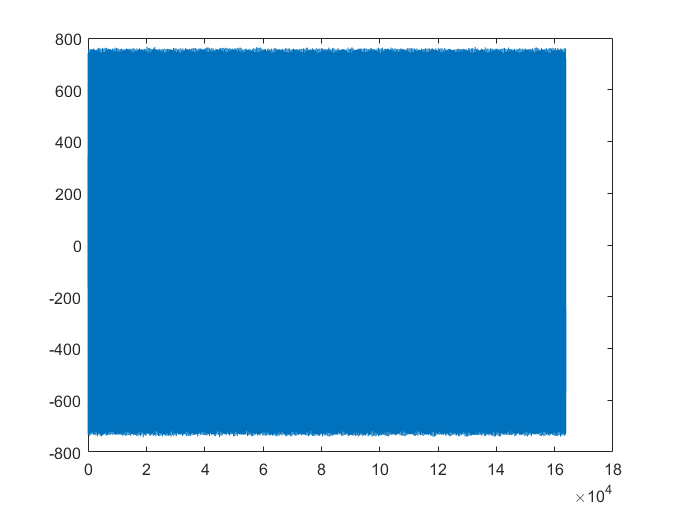

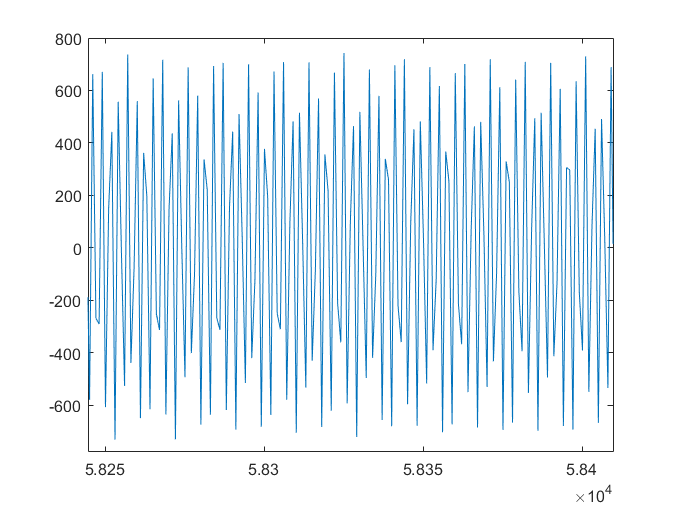

ADC1 data looks like AM (amplitude modulation signal but not constant sine wave from Signal Tap by setting the display to signed line. It's the same when plot the exported data in the time domain using MATLAB.

I need help about why is like this. Did I missing anything in configured ADC. Please note that the front end (ADC input) is the same as the EVM. Thank you.