help getting started with ADS7950

i have not been able to find command sequence examples that would fit our application and would appreciate a command snippet showing how we can accomplish our sampling

application:

we want to select a given channel, wait for an external trigger event to start collecting N samples at 100ksps then select the next arbitrary channel and wait for the next external trigger event to start

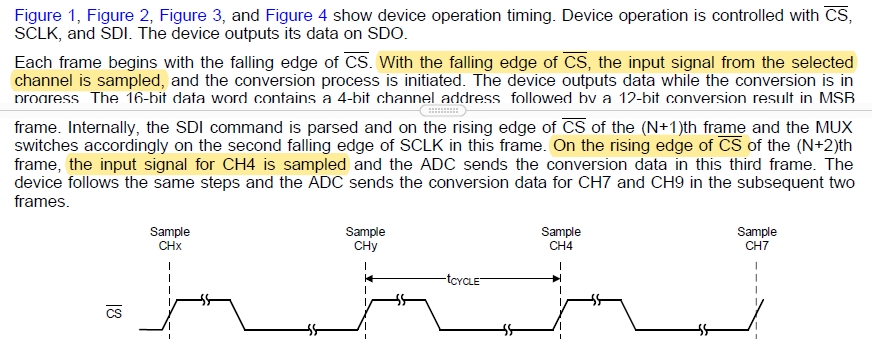

we plan to timestamp the first sample with our external trigger event by syncing with the CS falling edge. assuming that the falling edge of the CS acquires the sample and starts the conversion.

we are using external 2.5V reference but want the input range at 2xVref

the datasheet says 2 frames are needed to configure ic before the sample data is clocked out. does that mean that it is still possible to get consecutive data after each frame if nothing else changes?

it seems manual mode may best suit our application but would like to confirm.

beyond what is mentioned above, we are not making use of any other features the device offers.

thanks for your help.

Tom Greene