Hi Team,

I am using ADS1248 for temperature measurement using an RTD. I am receiving data from ADS1248 successfully. But always my very first conversion result is showing a wrong value. I connected a fixed resistance of 100 ohm instead of RTD for debugging. As a result I am observing a value like '6467667' or '6568120' as my first result. Later on I am getting values like '6217041' or '62170248' as conversion results from ADS1248. After the first result, the result is stable at a value within range of '6200000' which is more correct. That is when converted back to resistance, values in this range is more close to 100 ohm. I am always getting first result in the range of '6400000' and later on the values will be in the range of '62000000'. I am attaching the code below. Can you please tell me what is happening here. Since if this happens for every first reading after an input channel change then it will be a large problem for my code.

//*****************************************************************************

// FILE NAME : C_138 SPI loop back Test.c

// DATE : 20.05.2020

// AUTHORS : Vineeth N

// DESCRIPTION : FOR TESTING SPI OF C_138 USING RTD

// CONTROLLER CARD : Contoller 138 control Board

//******************************************************************************

/* EXTERNAL CRYSTAL FREQUENCY 20MHz

*******************************************************************************/

//-----------------------------------------------------------------------------

// Include Header Files

// ----------------------------------------------------------------------------

#include"F28x_Project.h"

void main(void)

{

int32 r1 = 0x00000000, r2 = 0x00000000;

// Initiate system controls, GPIO pins, interrupt

InitSysCtrl();

InitGpio();

EALLOW;

GpioCtrlRegs.GPAGMUX1.bit.GPIO9 = 1;

GpioCtrlRegs.GPAMUX1.bit.GPIO9 = 3; // set Gpio pin 9 as SPI clock pin

GpioCtrlRegs.GPAPUD.bit.GPIO9 = 0; // Pull up enable

GpioCtrlRegs.GPAQSEL1.bit.GPIO9 = 3; // Qualifier Selection

GpioCtrlRegs.GPAGMUX1.bit.GPIO8 = 1;

GpioCtrlRegs.GPAMUX1.bit.GPIO8 = 3; // set Gpio pin 8 as SPI SIMO pin

GpioCtrlRegs.GPAPUD.bit.GPIO8 = 0; // Pull up enable

GpioCtrlRegs.GPAQSEL1.bit.GPIO8 = 3; // Qualifier Selection

GpioCtrlRegs.GPAGMUX1.bit.GPIO10 = 1;

GpioCtrlRegs.GPAMUX1.bit.GPIO10 = 3; // set Gpio pin 10 as SPI SOMI pin

GpioCtrlRegs.GPAPUD.bit.GPIO10 = 0; // Pull up enable

GpioCtrlRegs.GPAQSEL1.bit.GPIO10 = 3; // Qualifier Selection

GpioCtrlRegs.GPAGMUX1.bit.GPIO14 = 0;

GpioCtrlRegs.GPAMUX1.bit.GPIO14 = 0; // set Gpio pin 14 as GPIO output pin (CS/)

GpioCtrlRegs.GPADIR.bit.GPIO14 = 1; // set direction as output

GpioCtrlRegs.GPAGMUX1.bit.GPIO15 = 0;

GpioCtrlRegs.GPAMUX1.bit.GPIO15 = 0; // set Gpio pin 15 as GPIO output pin (START)

GpioCtrlRegs.GPADIR.bit.GPIO15 = 1; // set direction as output

GpioCtrlRegs.GPBGMUX1.bit.GPIO34 = 0;

GpioCtrlRegs.GPBMUX1.bit.GPIO34 = 0; // set Gpio pin 34 as GPIO output pin (ADC_RST)

GpioCtrlRegs.GPBDIR.bit.GPIO34 = 1; // set direction as output (ADC_RST)

GpioCtrlRegs.GPAGMUX1.bit.GPIO6 = 0; // IRQ_3

GpioCtrlRegs.GPAMUX1.bit.GPIO6 = 0;

EDIS;

GpioDataRegs.GPACLEAR.bit.GPIO15 = 1; // START pin LOW

GpioDataRegs.GPASET.bit.GPIO14 = 1; // Clear CS/ pin to high

GpioDataRegs.GPBSET.bit.GPIO34 = 1; // ADC Reset disabled

// SpiaRegs.SPIFFTX.all = 0xE040;

// SpiaRegs.SPIFFRX.all = 0x2044;

// SpiaRegs.SPIFFCT.all = 0x0;

SpiaRegs.SPIFFTX.bit.SPIRST = 1; // SPI Reset. SPI FIFO can resume transmit or receive. No effect to the SPI registers bits.

SpiaRegs.SPIFFTX.bit.SPIFFENA = 1; // SPI FIFO Enhancements Enable

SpiaRegs.SPIFFTX.bit.TXFIFO = 1; // Release transmit FIFO from reset.

SpiaRegs.SPIFFTX.bit.TXFFINTCLR = 1; // TXFIFO Interrupt Clear. Write 1 to clear SPIFFTX[TXFFINT] flag

SpiaRegs.SPIFFTX.bit.TXFFIENA = 0; // TX FIFO interrupt based on TXFFIL match (less than or equal to) will be disabled.

SpiaRegs.SPIFFTX.bit.TXFFIL = 0; // A TX FIFO interrupt request is generated when there are no words remaining in the TX buffer

SpiaRegs.SPIFFRX.bit.RXFFOVFCLR = 1; // Receive FIFO Overflow Clear. Write 1 to clear SPIFFRX[RXFFOVF].

SpiaRegs.SPIFFRX.bit.RXFIFORESET = 1; // Re-enable receive FIFO operation.

SpiaRegs.SPIFFRX.bit.RXFFINTCLR = 1; // Receive FIFO Interrupt Clear. Write 1 to clear SPIFFRX[RXFFINT] flag

SpiaRegs.SPIFFRX.bit.RXFFIENA = 1; // RX FIFO interrupt based on RXFFIL match (greater than or equal to) will be disabled.

SpiaRegs.SPICCR.bit.SPISWRESET = 0; // clear software reset bit

SpiaRegs.SPICTL.bit.MASTER_SLAVE = 1; // master mode selected

SpiaRegs.SPICTL.bit.CLK_PHASE = 0; // clock phase selection

SpiaRegs.SPICCR.bit.CLKPOLARITY = 0; // clock polarity

SpiaRegs.SPIBRR.bit.SPI_BIT_RATE = 24; //(25MHz/25 = 1 MHz)

SpiaRegs.SPICCR.bit.SPICHAR = 15; // character per transfer

SpiaRegs.SPISTS.bit.INT_FLAG = 1; // clear interrupt flag

SpiaRegs.SPISTS.bit.OVERRUN_FLAG = 1; // clear over run flag

SpiaRegs.SPIPRI.bit.FREE = 1;

SpiaRegs.SPICCR.bit.SPILBK = 0; // loop back disable

SpiaRegs.SPICTL.bit.TALK = 1; // slave talk enabled

SpiaRegs.SPICTL.bit.SPIINTENA = 0; // interrupt disable

SpiaRegs.SPICCR.bit.SPISWRESET = 1; // software reset disabled

GpioDataRegs.GPACLEAR.bit.GPIO14 = 1; // Clear CS/ pin to low

GpioDataRegs.GPASET.bit.GPIO15 = 1; // Enable the device by setting START pin high

DELAY_US(1);

SpiaRegs.SPITXBUF = 0xFF06; // Send the RESET command and wait for 0.6ms

// while (SpiaRegs.SPIFFTX.bit.TXFFINT !=1 ); // Wait until TXFIFO is empty

// SpiaRegs.SPIFFTX.bit.TXFFINTCLR = 1; // TXFIFO Interrupt Clear. Write 1 to clear SPIFFTX[TXFFINT] flag

DELAY_US(600);

// Register configuration of ADS1248

SpiaRegs.SPITXBUF = 0x1640; // Send the SDATAC command and WREG Command 1st byte

SpiaRegs.SPITXBUF = 0x030A; // WREG Command 2nd byte and MUX0 register value

SpiaRegs.SPITXBUF = 0x0020; // VBIAS register value and MUX1 register value

SpiaRegs.SPITXBUF = 0x444A; // SYS0 register and WREG 1st command byte

SpiaRegs.SPITXBUF = 0x0105; // WREG 2nd command byte and IDAC0 register value

SpiaRegs.SPITXBUF = 0x0304; // IDAC1 register value and NOP command

// while (SpiaRegs.SPIFFTX.bit.TXFFINT !=1 ); // Wait until TXFIFO is empty

// SpiaRegs.SPIFFTX.bit.TXFFINTCLR = 1; // TXFIFO Interrupt Clear. Write 1 to clear SPIFFTX[TXFFINT] flag

while(SpiaRegs.SPIFFRX.bit.RXFFST < 7 );

DELAY_US(2);

GpioDataRegs.GPASET.bit.GPIO14 = 1; // Clear CS/ pin to high

while(1)

{

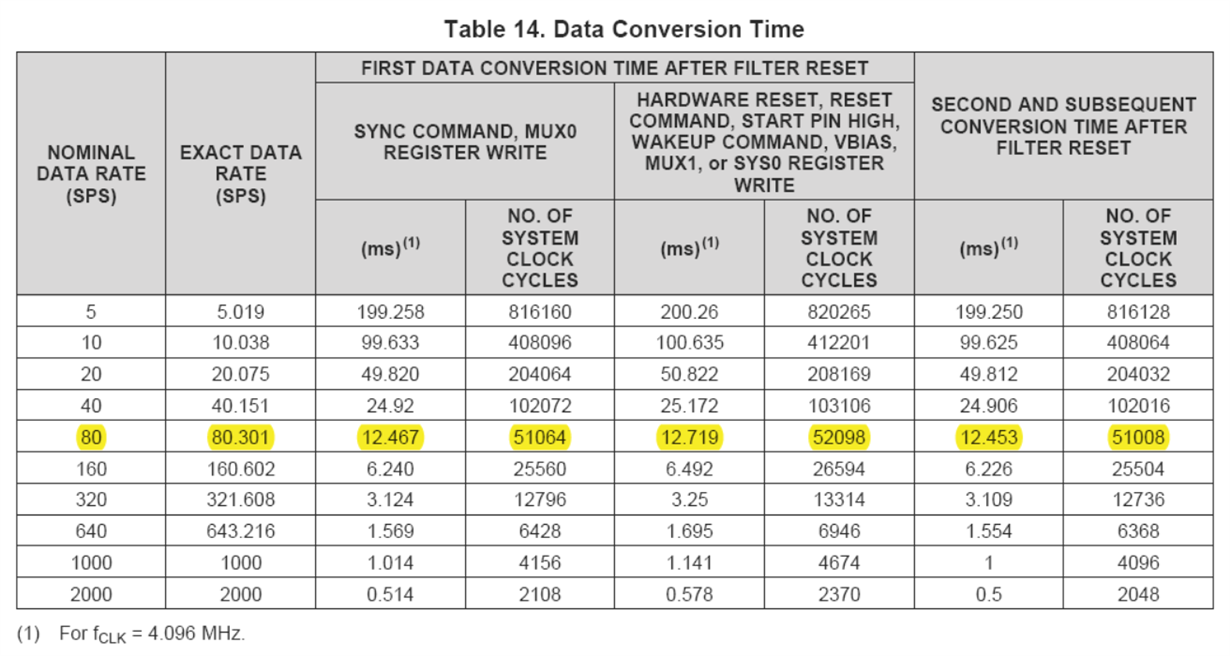

DELAY_US(13000);

GpioDataRegs.GPACLEAR.bit.GPIO14 = 1; // Clear CS/ pin to low

DELAY_US(1);

SpiaRegs.SPIFFRX.bit.RXFIFORESET = 0;

SpiaRegs.SPIFFRX.bit.RXFIFORESET = 1;

// Receive conversion result from ADS1248

SpiaRegs.SPITXBUF = 0xFF12; // NOP and RDATA

SpiaRegs.SPITXBUF = 0xFFFF; // NOP commands

SpiaRegs.SPITXBUF = 0xFF04; // NOP commands

while(SpiaRegs.SPIFFRX.bit.RXFFST < 3);

r1 = SpiaRegs.SPIRXBUF;

r1 = SpiaRegs.SPIRXBUF;

r1 = r1<<8;

r2 = SpiaRegs.SPIRXBUF;

r1 = r1|r2>>8;

DELAY_US(1);

GpioDataRegs.GPASET.bit.GPIO14 = 1; // Clear CS/ pin to high

}

}

Best Regards,

Vineeth N