Using and STM32 to control the DAC using SPI. I output does not change with messages, and reading DEVICE ID always gives corrupt data.

Procedure

- /CS

- Send GAIN configuration message (0x04,0x01,0x0F)

- CS

- /CS

- Send OUT0 DATA output request (0x08,0x0F,0xFF)

- CS

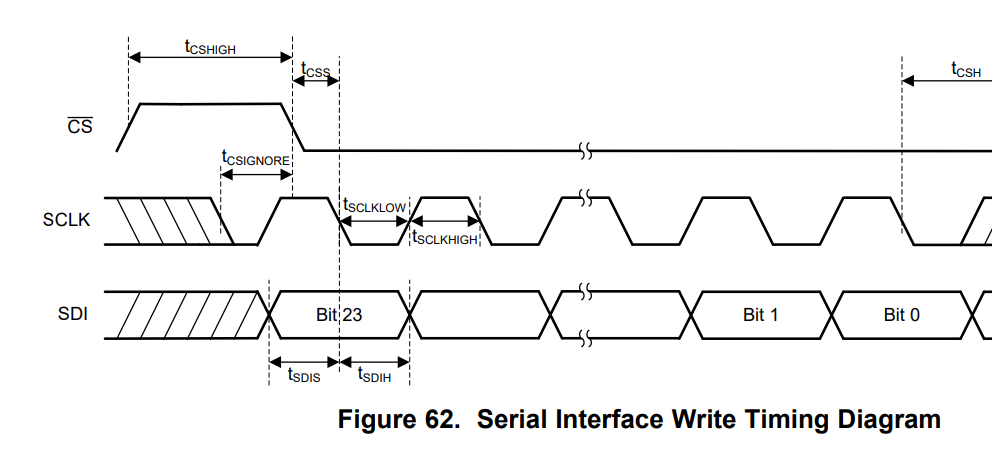

Writing is done to be sampled at CLK falling edge, as DIO spec says.

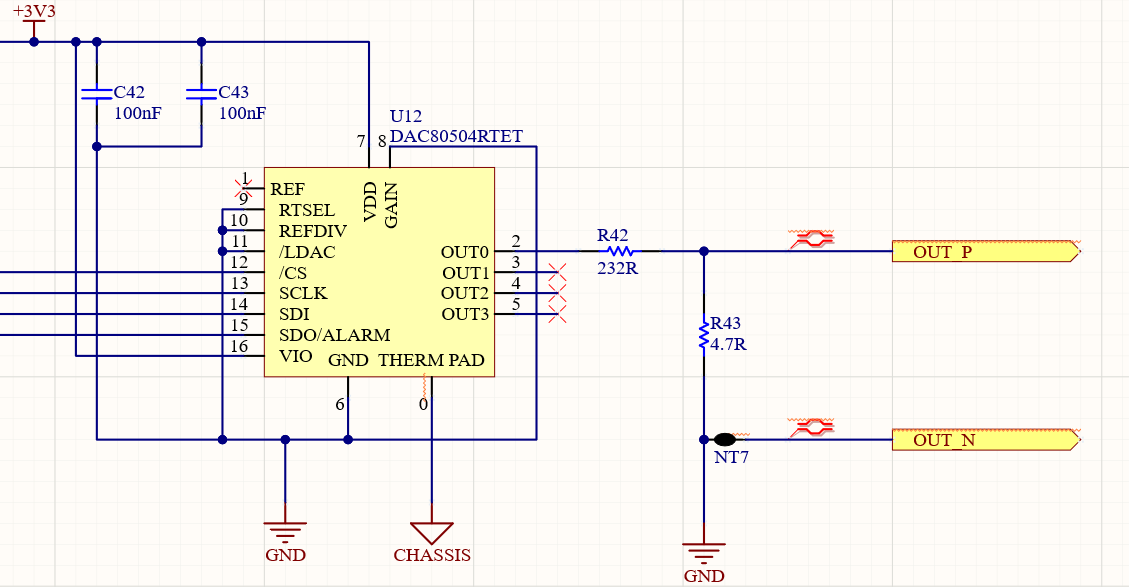

Wiring

Signals coming into the device are confirmed to be properly routed.

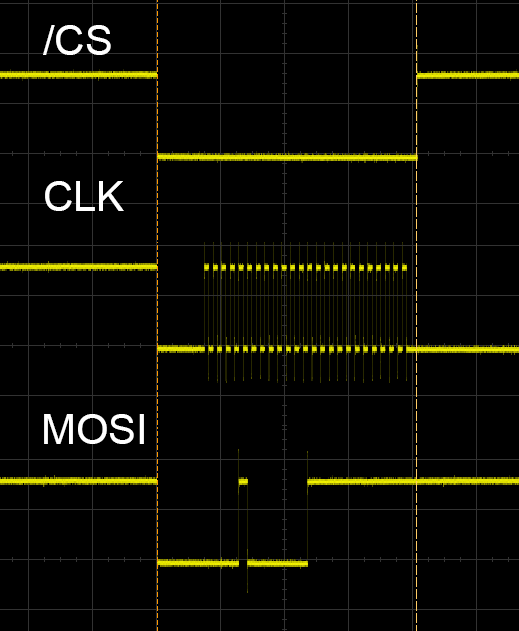

SPI Signals

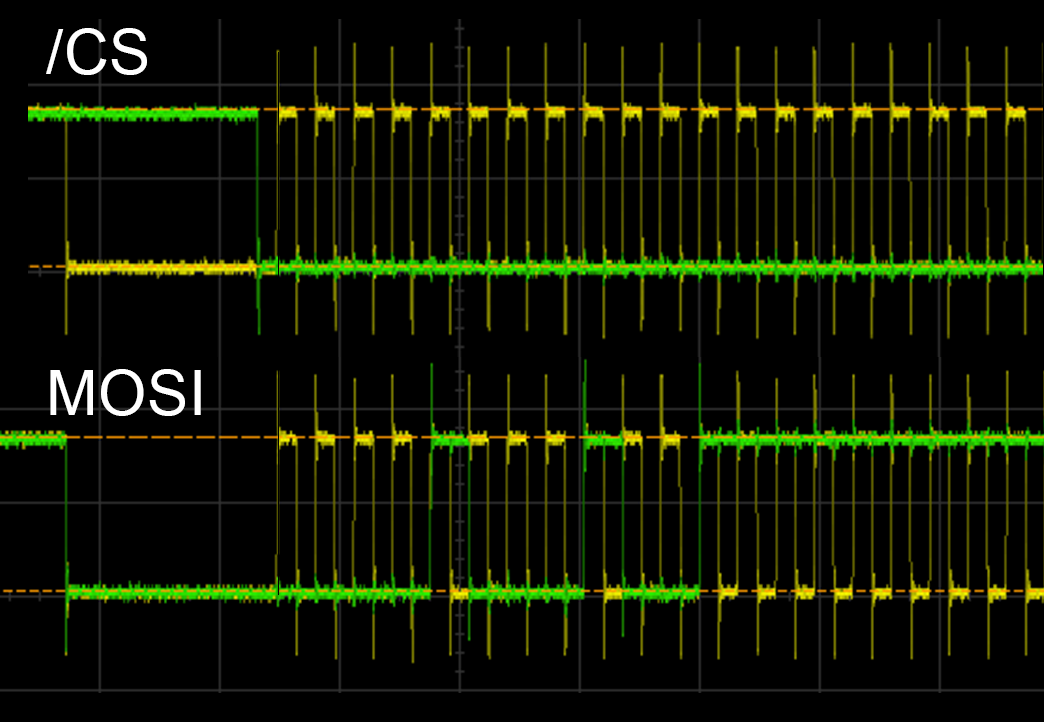

overlay of /CS, CLK, and DATA. Data is sent MSB (bit 23 received first, and containing R/W message type)

Has anyone encountered an issue with this before, or am I missing something. Any help would be appreciated.

Thanks

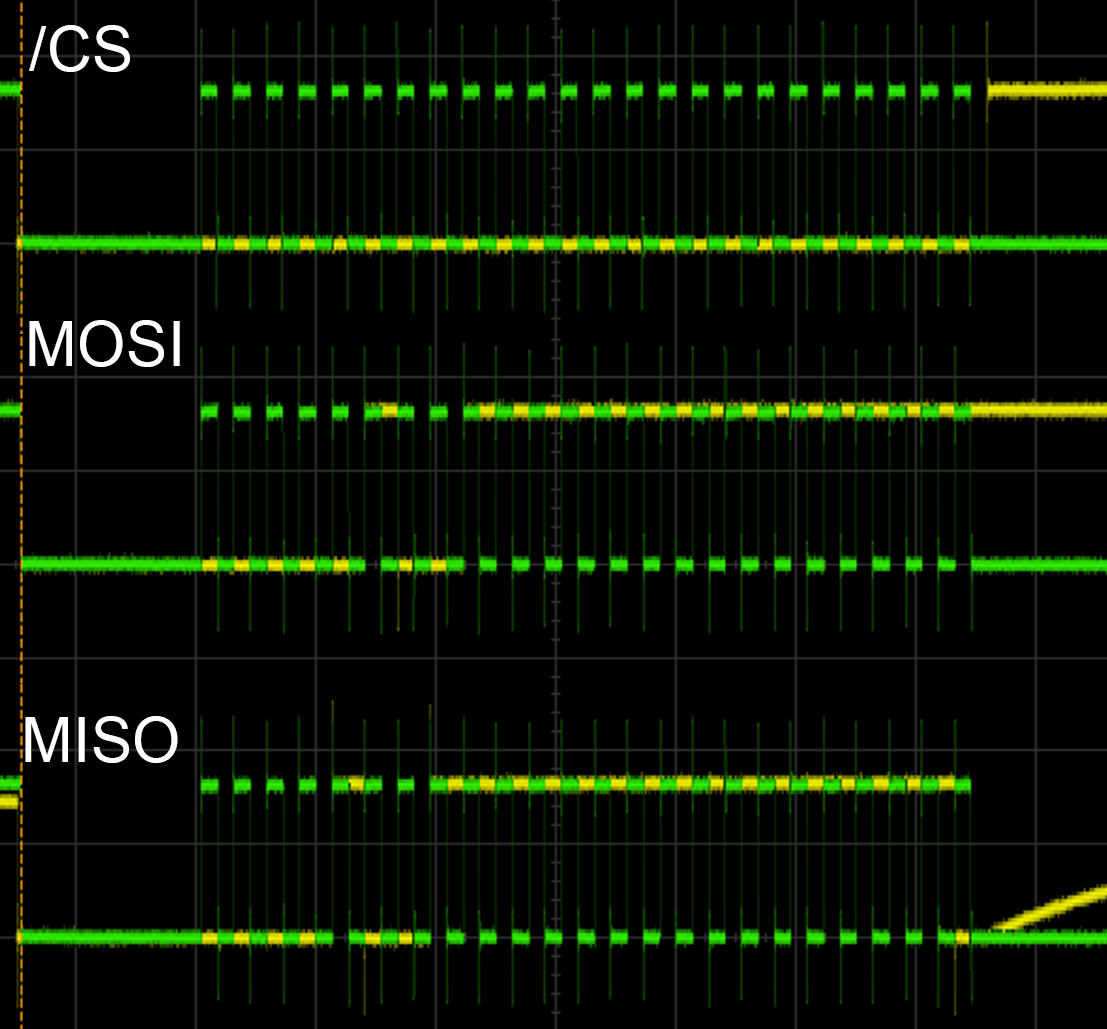

UPDATE

I ran some trace tests and it looks like the first bit of the transmission is always ignored by the DAC. I capture the trace of the DAC SDO and the echo is always shifted one bit to the left, removing the 1st bit and moving everything else over.

Changing my dataframe on the STM32 to fix this issue still eliminates the ability to read (first bit is never read by the DAC).