Other Parts Discussed in Thread: DAC8551, DAC8550

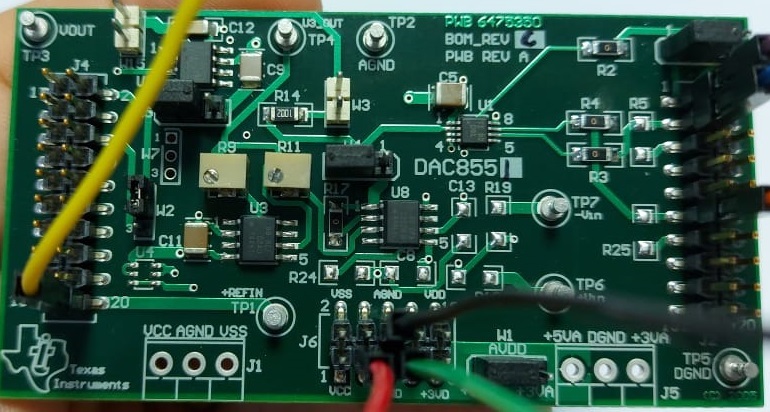

I have DAC8551 Evaluation Module connected with TC-399 evaluation kit to drive analog voltage, I have connected DAC8551 Evaluation Module pins as following:

- Supply Voltage:

- J6-3: +5V (Vdd)

- J6-5: Gnd

- J6-6: Gnd

- J4-20: +5V (Vref)

- Jumper Setting Function Connections:

- W1: +5-V analog supply is selected for AVDD.

- W2: (1-2) Routes VOUTA to J4-2.

- W3: (Not connected) Disconnects VREFH to the inverting input of the output operational amplifier, U2

- W4: (3-2) Routes the user-supplied reference from U4 (if installed), TP1 or J4-20 to the VREFH input of the DAC8550/51/52.

- W5: (1-2) Negative supply rail of the output operational amplifier, U2, is powered by VSS for bipolar operation.

- W6: (1-2) CS signal from J2-1 is routed to drive the SYNC signal of the DAC8550/51/52.

- W7: (Not found) This is the default jumper position for DAC8550/51EVM when R1 is installed.

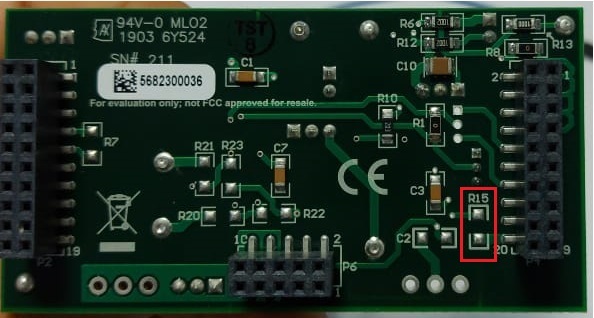

- W15: (Not connected) Disconnects the inverting input of the output operational amplifier, U2, from the gain resistor, R12.

- Serial Header Connections:

- J2-1: QSPI_CS of the MCU.

- J2-3: QSPI_SCLK of the MCU.

- J2-11: MTSR (SDI) of the MCU.

After done with this connections I run the software and transmit Din = 32768 to get Vout = +5V, but Vout still equal zero and I tried many values for Din and Vout still zero.

I expect output from J4-2 pin.

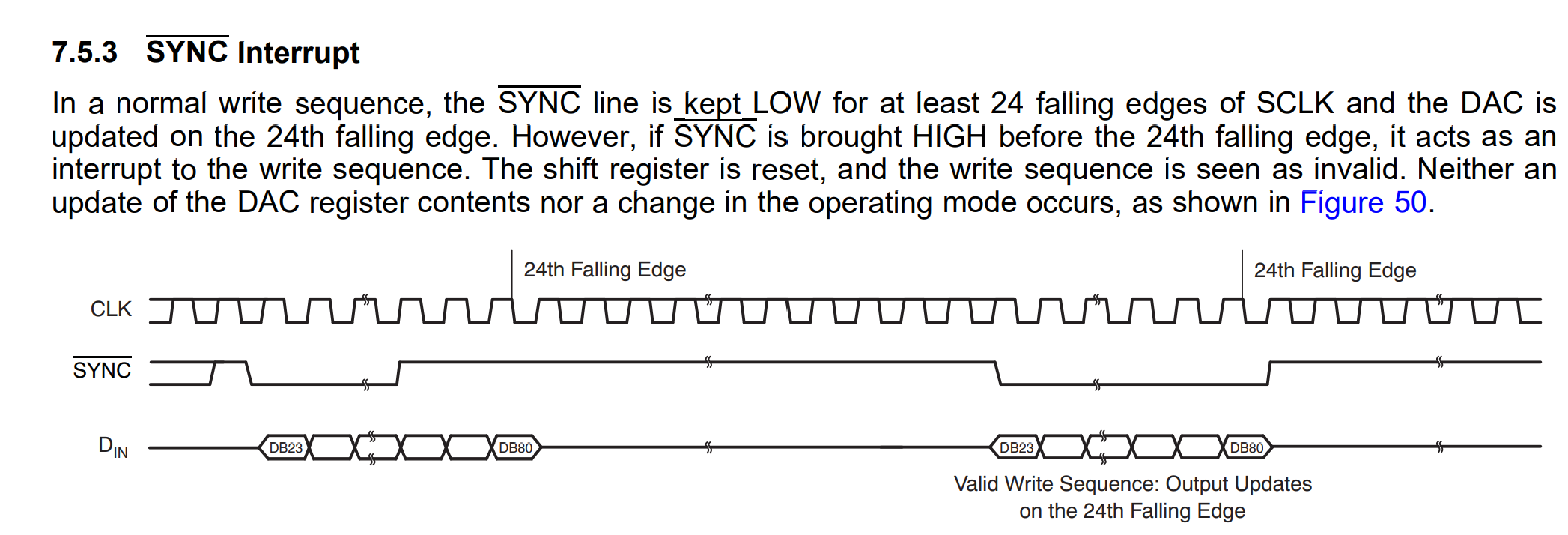

Note the QSPI output is tested and here is the output:

Could you please tell me if I have fault in connection or in using the evaluation module and help me to operate evaluation module to get the desired Vout.

Note: (I didn't use the operational amplifier so I expect Vout from J4-2 pin to get the DAC output before using the Op-amp also I didn't connect the VCC and VSS of Op-amp because I expect the output just after the DAC conversion)