Other Parts Discussed in Thread: ADC12DJ3200

Hi team,

Another customer asked about ADC12DJ5200RF, sorry to disturb you again.

The customer problem is described as follows:

1. ADC is ADC12DJ5200RF and configured as JMOD1. The code of Transport Layer is written with reference to the example project of ADC12DJ3200. After careful check, no problem is found.

2. When JTEST=Ramp test mode, the data read out is correct, indicating that the link is correct.

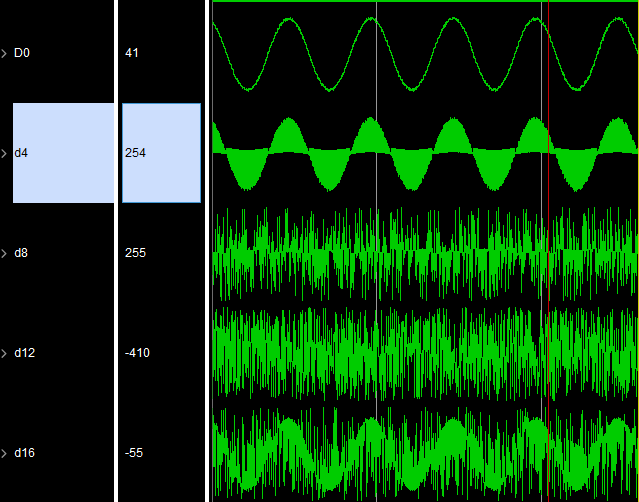

3. After changing to JTEST=nomal mode, it is found that only part of the output waveform of the Transport Layer is correct sine wave (the output is 240bit, divided into 20 channels * 12bit), and the rest are wrong. Some waveforms are as follows

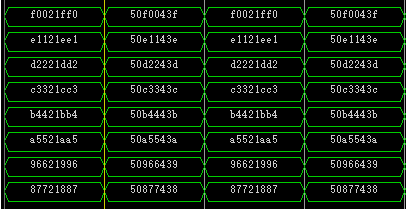

4. In order to locate the problem, I configure JTEST=Transport Layer test mode, observe the data received by lane0 ~ lane7, and see that the test data is wrong. It is different from the description in table 61. Short transport test pattern for n '= 12, f = 8 modes (length = 1 frame) in the datasheet. It seems that the data is just misplaced

As shown in the figure: (From top to bottom, it corresponds to DA0 ~ DA7 of table 61)

The difference between Transport Layer test mode and Ramp test mode is whether the Transport Layer is included. Does this mean that there is something wrong with the Transport Layer? What are the possible causes?