Other Parts Discussed in Thread: ADC12DJ3200, ADC12DJ3200EVM, ADC34J45

Hello,

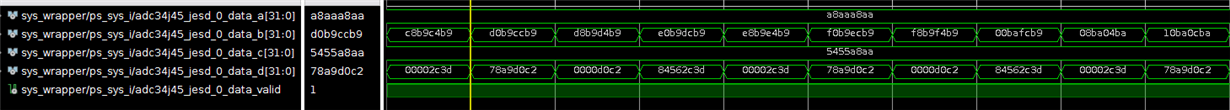

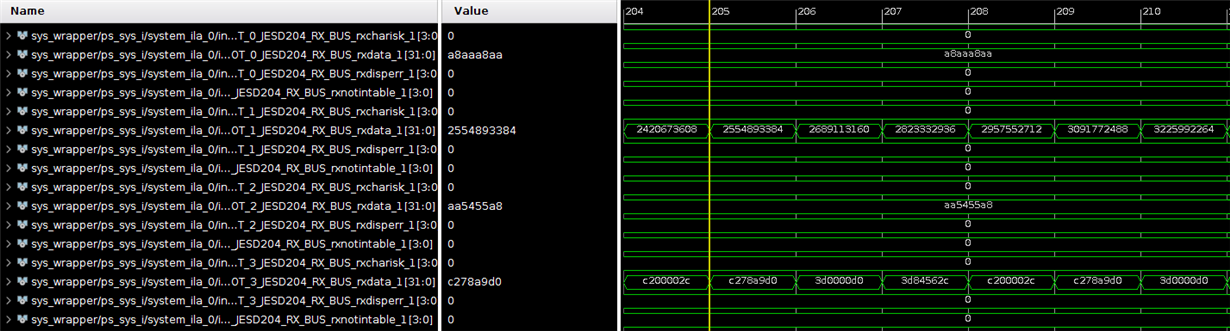

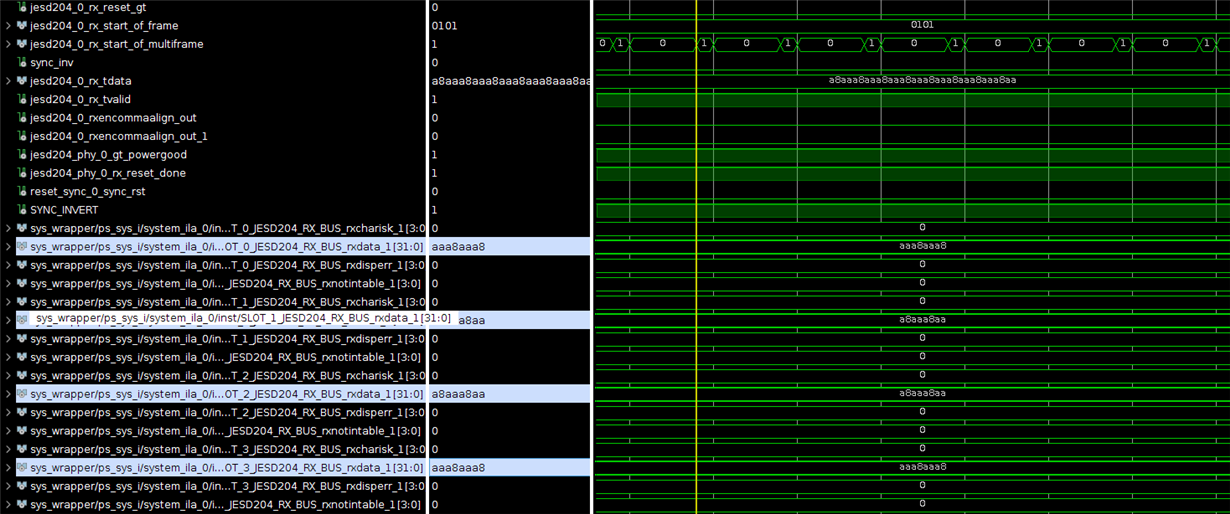

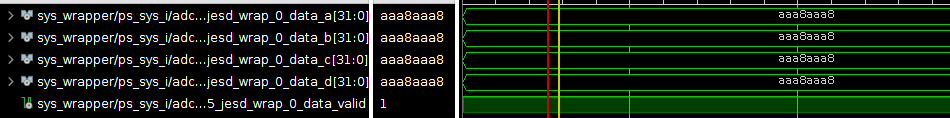

I previously posted a question about SPI configuration for the ADC34J45EVM, and now I'm having some problems trying to implement the JESD204B interface itself. I'm using the Xilinx JESD204 IP cores, and tried interfacing to the EVM in Subclass 0, 20x mode (LMFS= 4421), 3.2 Gbps, at 160 MSPS. The FPGA RX is configured as:

- L=4,F=2,K=8

- The core clock (x40) is at 80MHz, and is derived from the 320MHz clock the LMK generates for the transceivers.

- SYSREF is sampled at the positive edge

- Core re-aligns LMFC counter on all SYSREF events

- SYSREF is not required after re-SYNC (RX core deasserts SYNC on the next LMFC)

I think configured the Xilinx IP cores correctly (I have made a similar post on the Xilinx forum, so I think I'll get confirmation/corrections soon), but I cannot get the link to work properly (it sometimes achieves SYNC briefly, but keeps losing). The basic steps my system goes through are:

- Configure the EVM through SPI, following one of the config files provided by TI (ADC3xJxx_160MSPS_Operation_LMK_Setting.cfg)

- Reset JESD IP cores

- Write write AXI config to IP cores

- Soft reset the IP

I'm quite new to JESD204B, so I'm not sure if I made any obvious mistake. Also, I'm not very familiar with the LMK chips. With that in mind, questions are:

- Am I correct in assuming I can simply follow the .cfg when programming the LMK? In the SPI configuration step, I simply configure the registers as described by the file, in the same order. Looking at the datasheet, it seemed very complex (and my chronogram is tight), so I'm trying this simplistic approach to at least get the link working before delving into the LMK details. I'm aware that simply blindingly following some file is... unusual, so I'm expecting there might be something more

- Is this configuration achievable? The Xilinx IP work in x40 rate exclusively. I'm new to JESD204, so I'm not sure if this is compatible with the x20 mode in the ADC. Although from what I understand there seems to be nothing prohibiting this, I'm not confident enough in this.