Hello,

My setup is as follows:

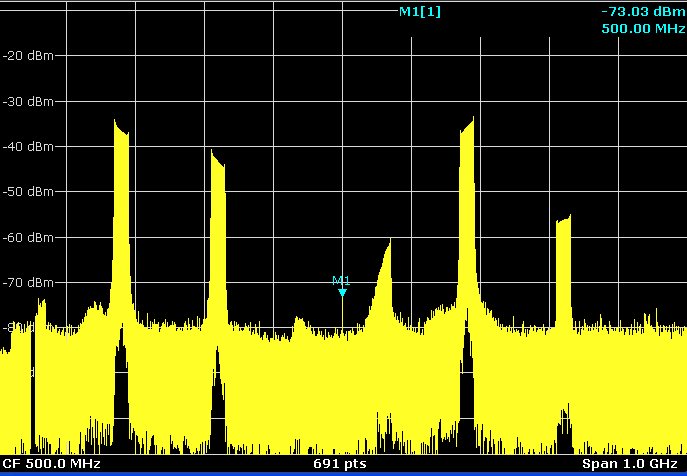

1) DAC chA data input: cosine @ 10MHz (full scale 16 bit, 10MHz output level (i.e., without NCO) is ~2dBm

2) DAC chB data input: sine @ 10MHz

3) NCO set to 400MHz, complex mixer enabled.

Problem: Image rejection : The image rejection is only 15dB. Also, the NCO freq (carrier) is completely eliminated (is this normal).

The NCO output is at -20dBm, seems low; is this expected. Please provide some reference for the calculation.

Please advise,

Output spectrum of chA