Other Parts Discussed in Thread: DAC80504, OPA627,

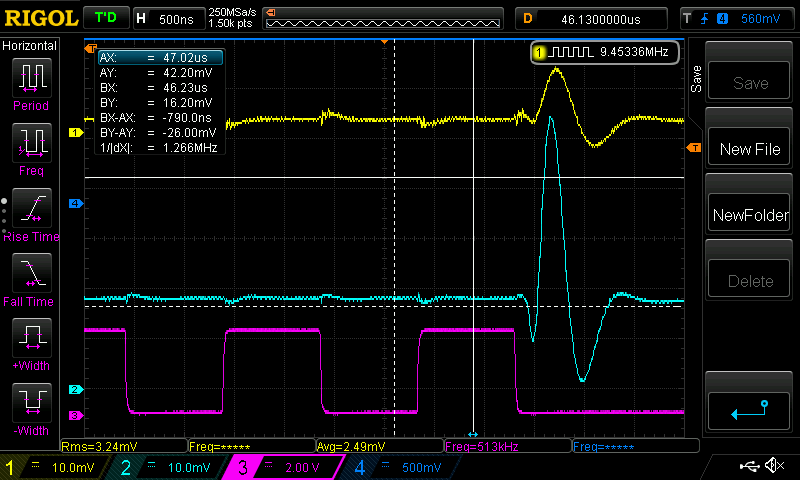

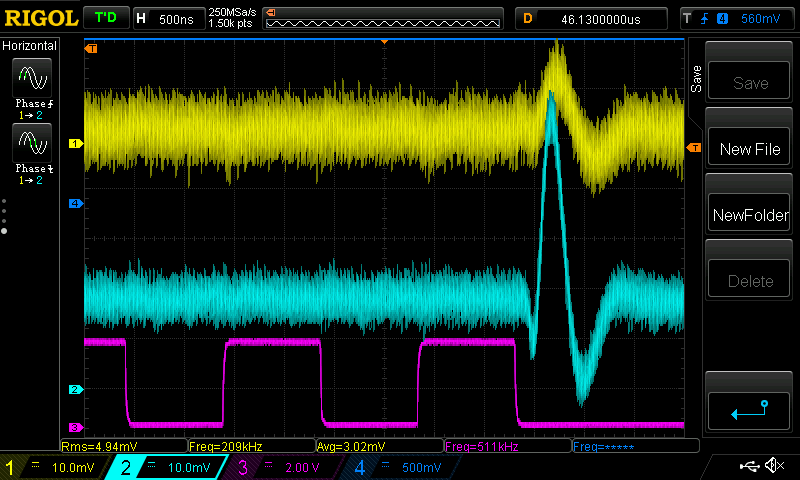

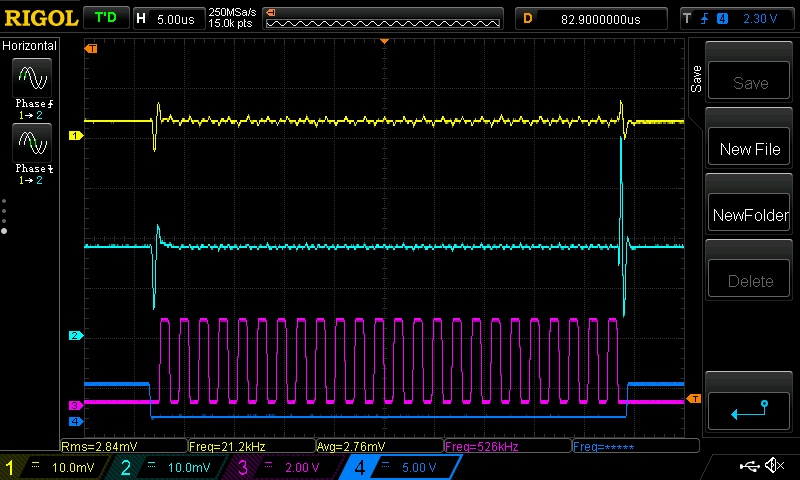

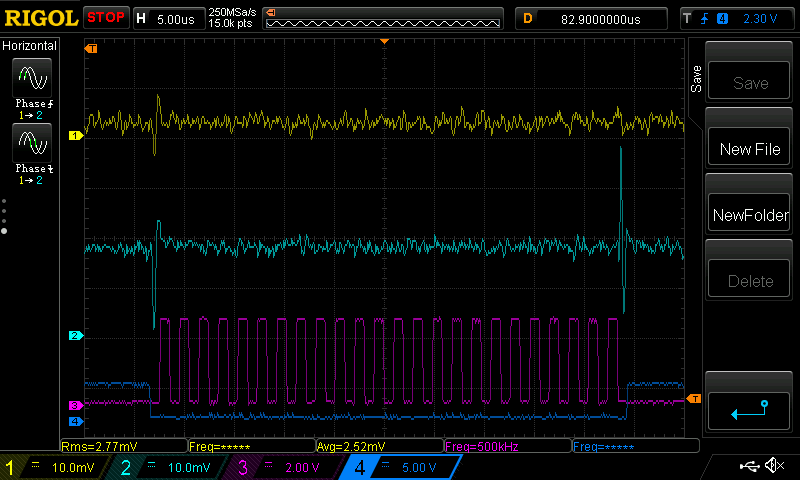

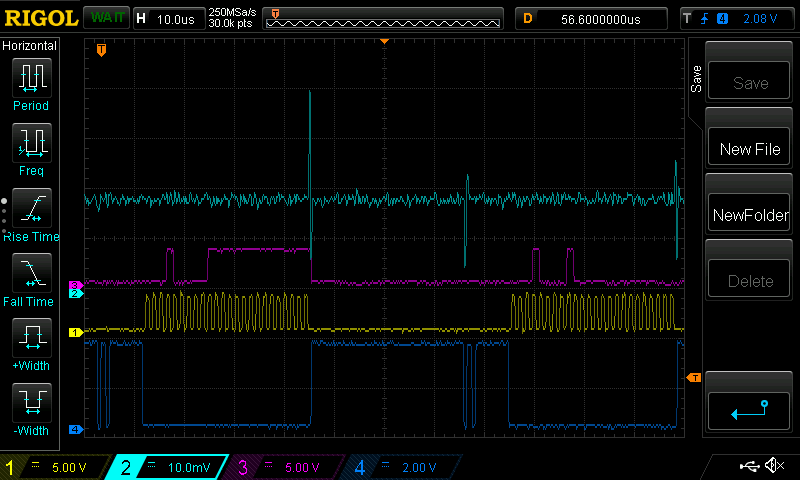

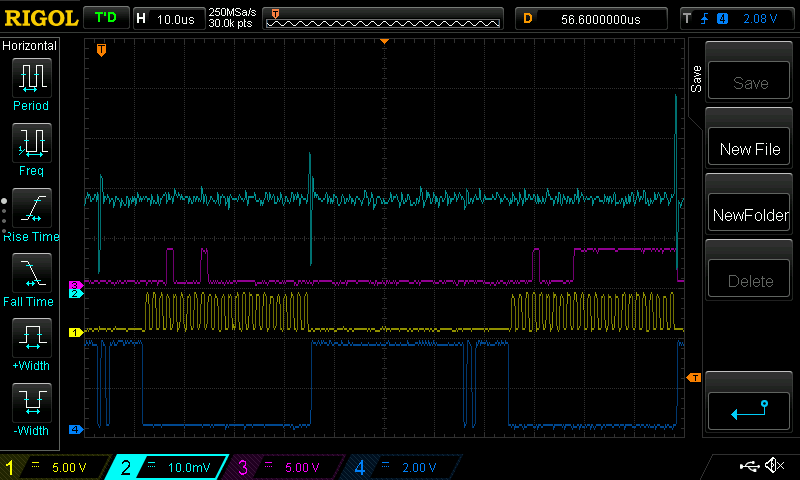

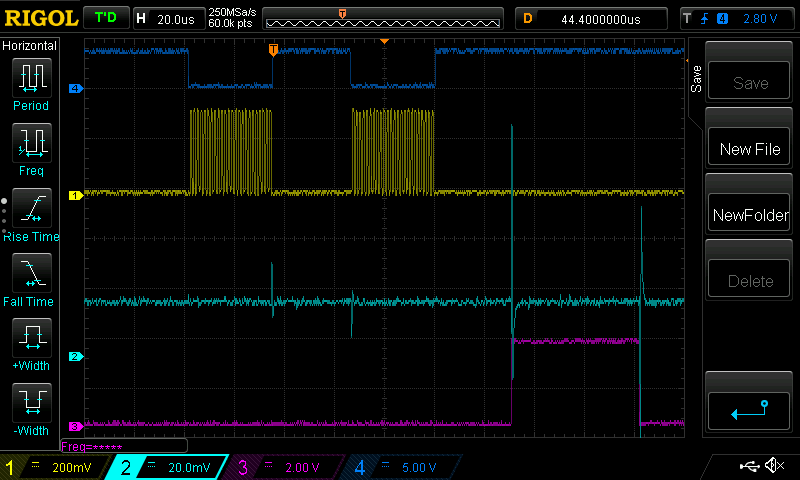

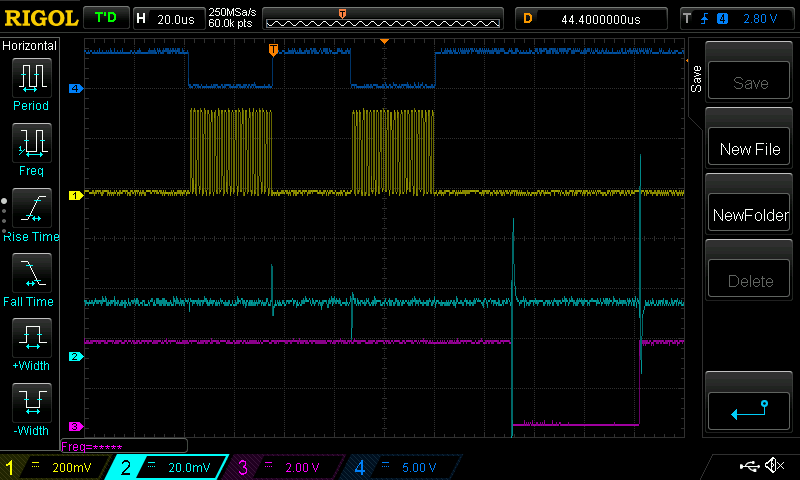

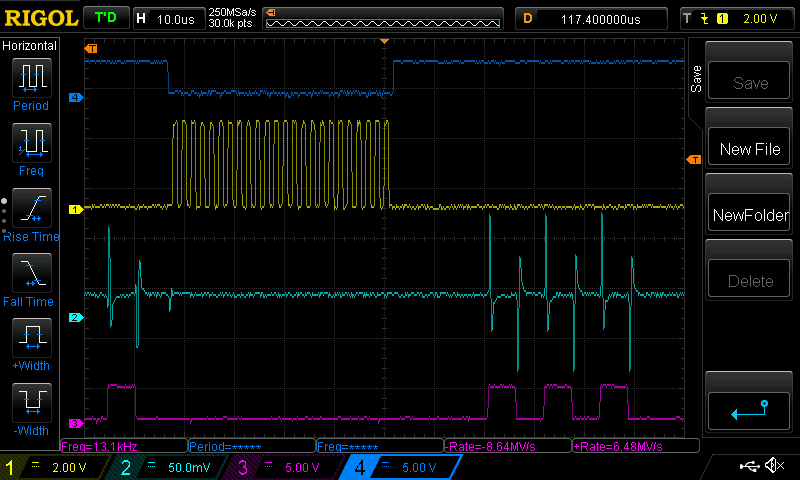

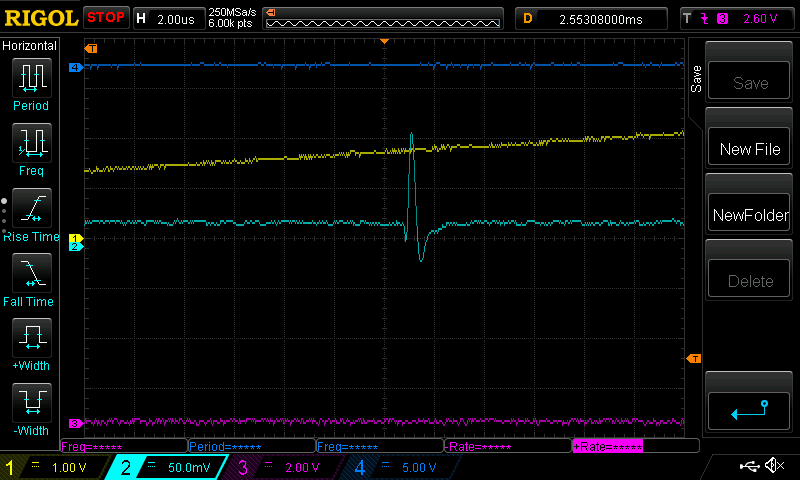

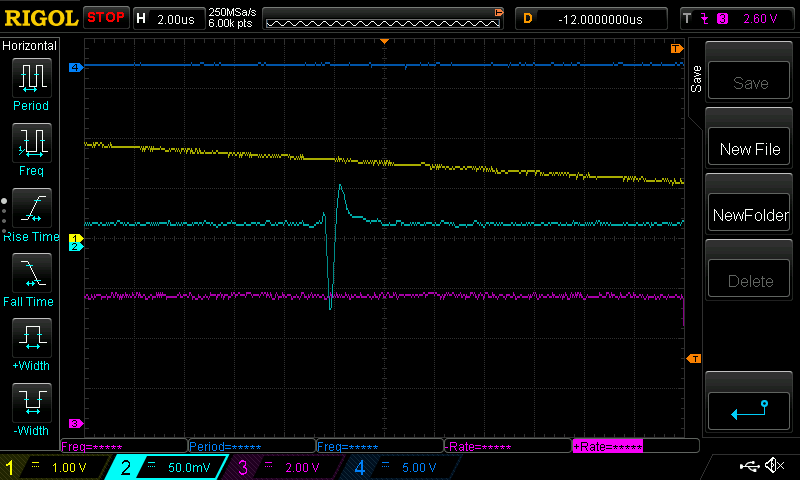

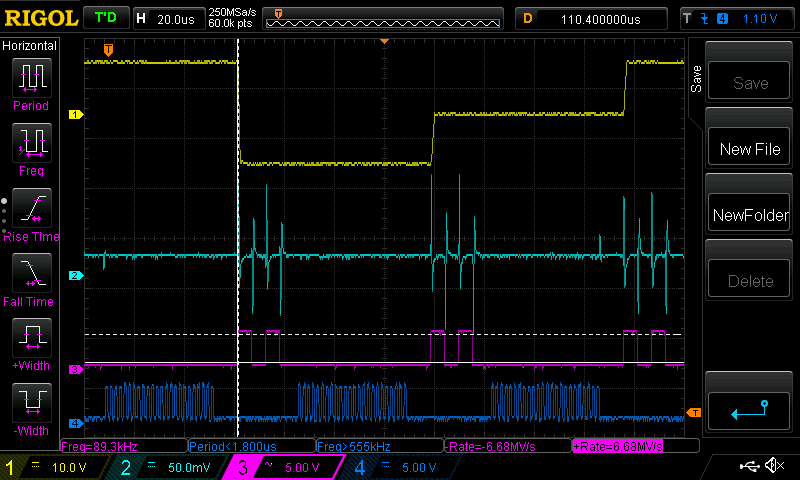

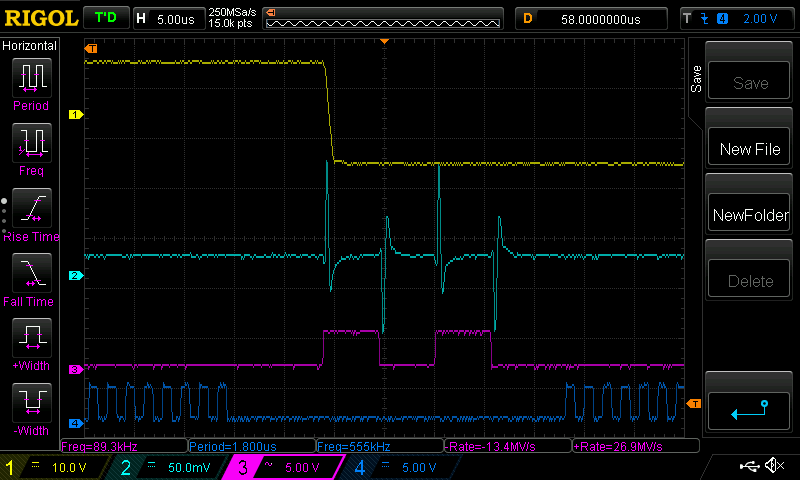

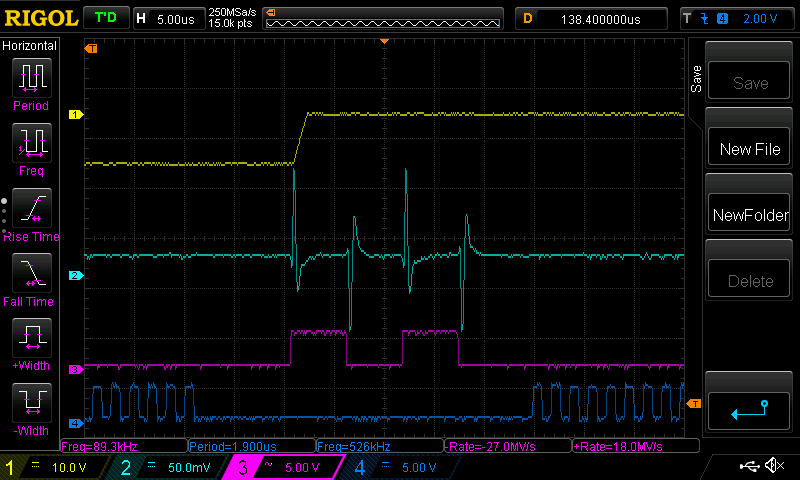

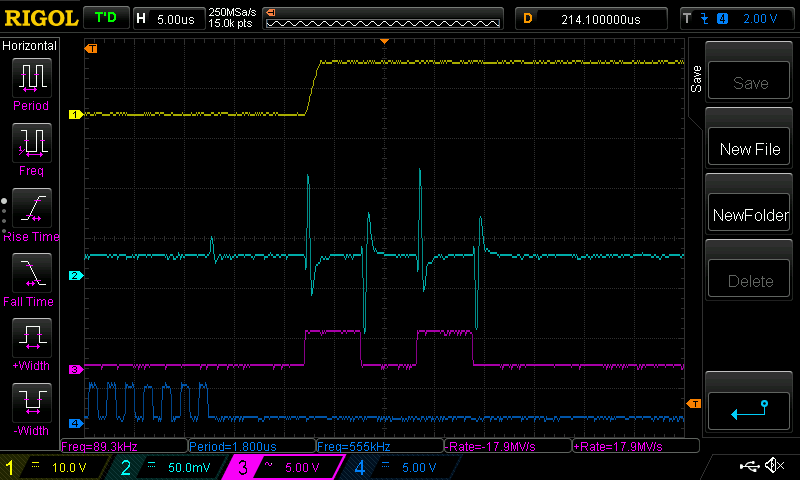

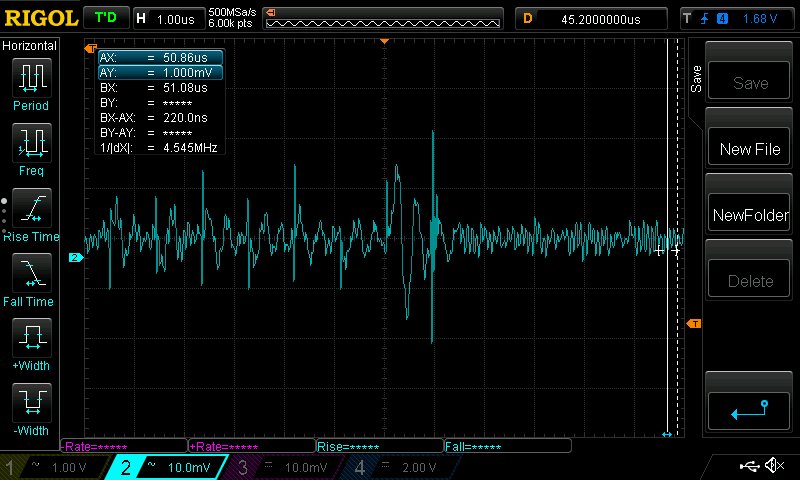

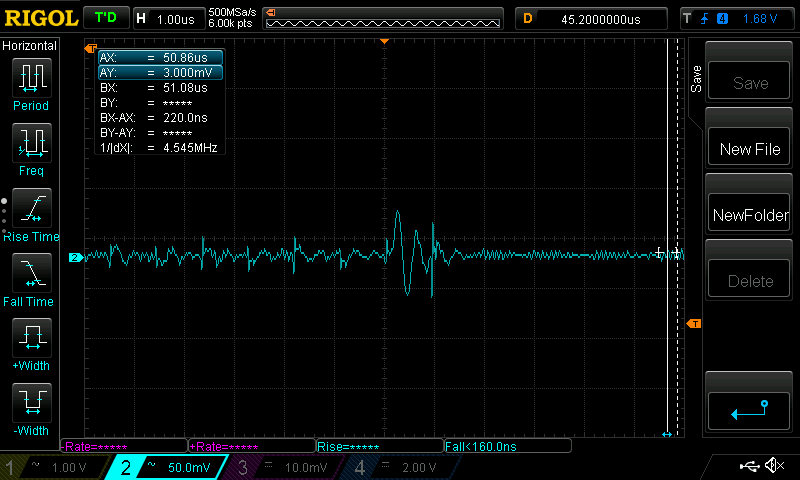

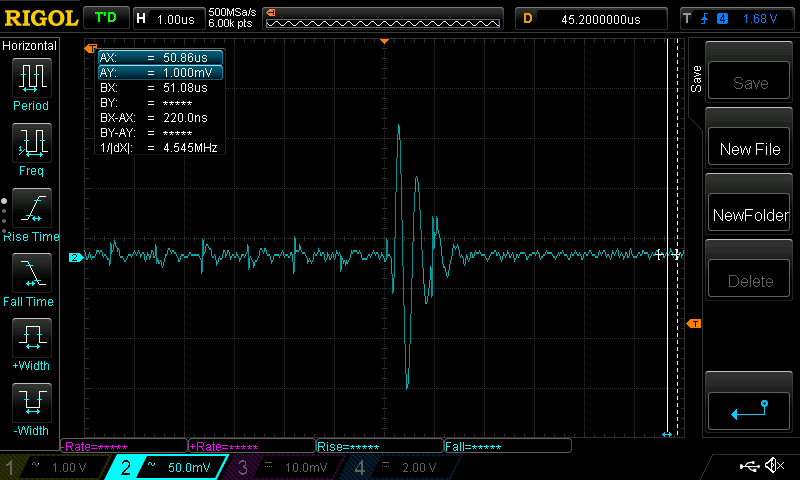

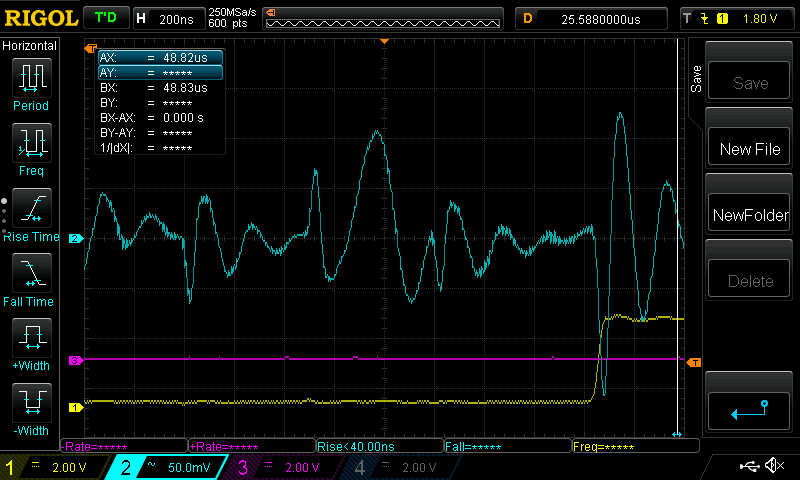

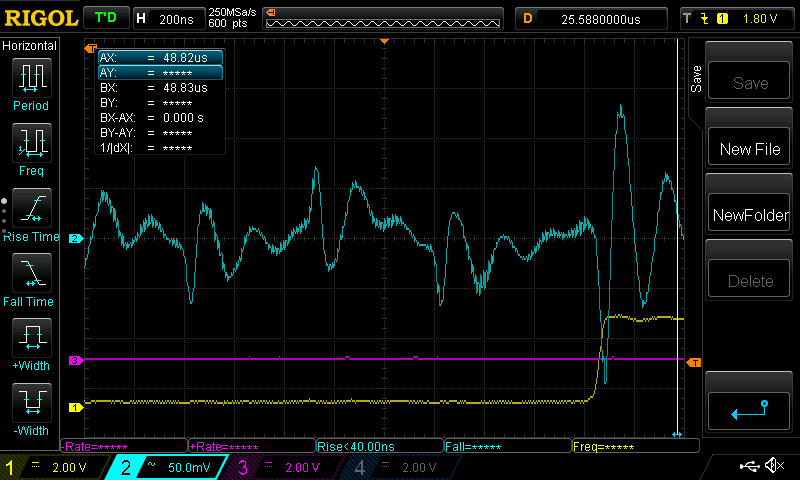

I'm trying to understand the glitch energy on the DAC8554 better as I'm seeing higher than expected glitching and different results on different channels. When trying to recreate figure 35 in the datasheet, I observe that the glitch energy is not a function of LDAC (soft or hard) but happens whenever the data buffer (not DAC register) is updated. Also, I see the same glitch on all channels, regardless of which one is being written to. For example, if I change the data buffer on channel B from 0x7FFF to 0x8000, I see glitch with the same amplitude on channels A, C and D as I see on channel B. Is this expected?

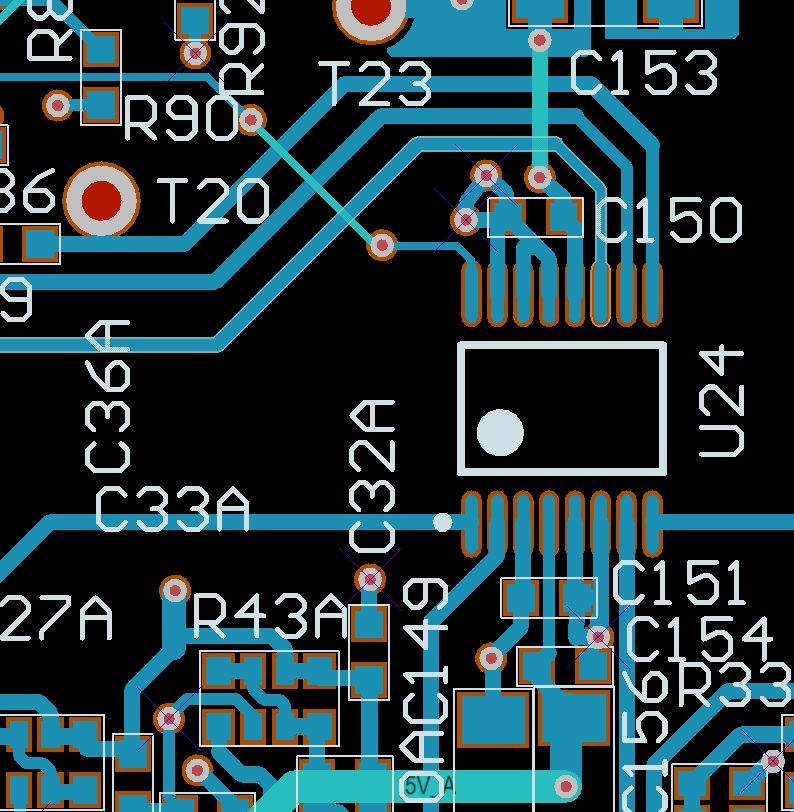

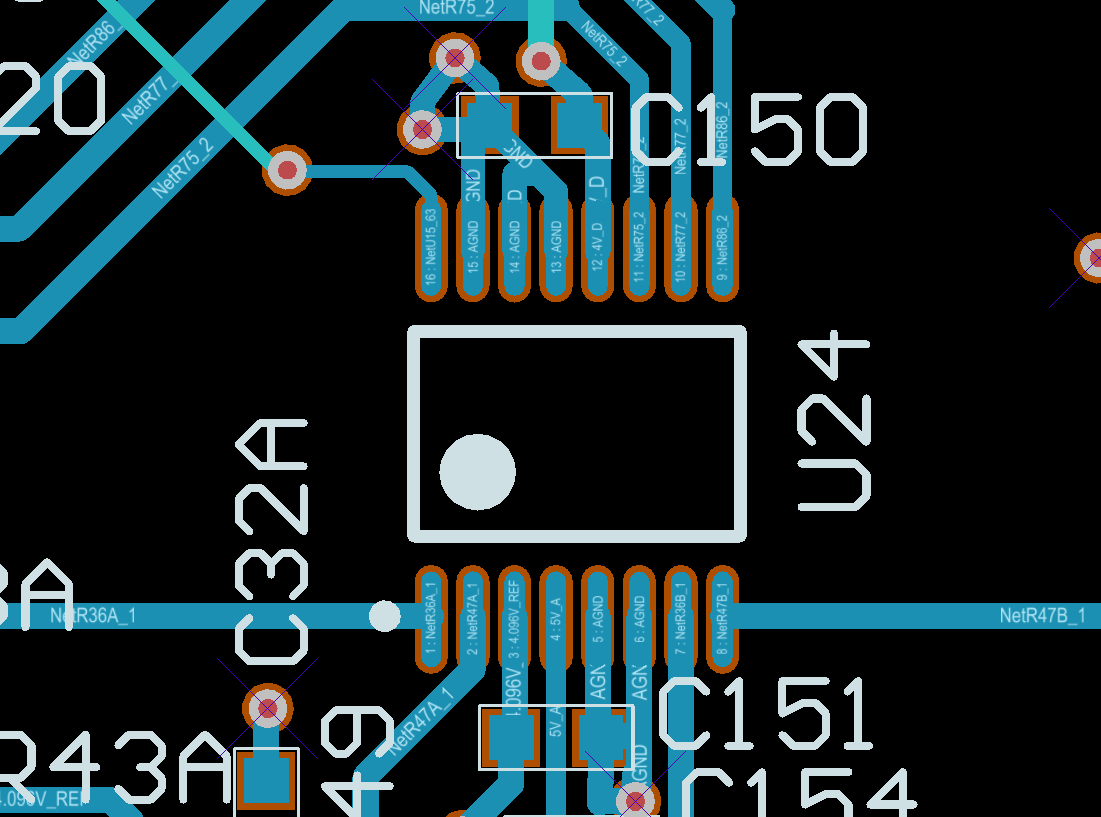

On my circuit, I'm seeing increased glitch energy on some channels. Specifically, when updating channel A data buffer, I see a bigger glitch on channel B. Also, when updating channel C, I see a big glitch on channel C than when updating other channels. Is there any reason to expect different channels to have larger glitches that other channels or be more sensitive to changes in other channels? If this is a layout issue, are there any layout recommendations to reduce glitching? Is all the glitching on the DAC output pins, or are there other pins / radiation (EMI) that contribute that I should be aware of for design and layout?

Thank you,

Ben