Other Parts Discussed in Thread: THS4561, THS4531,

Hi team,

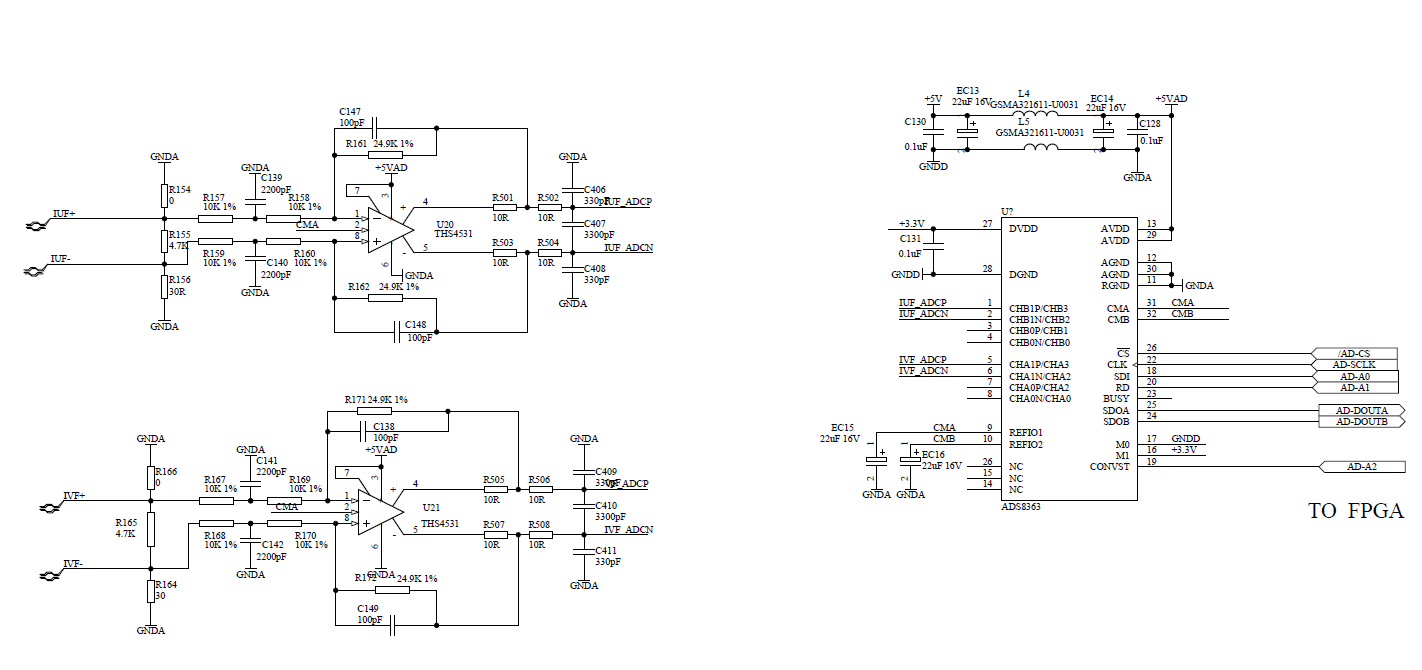

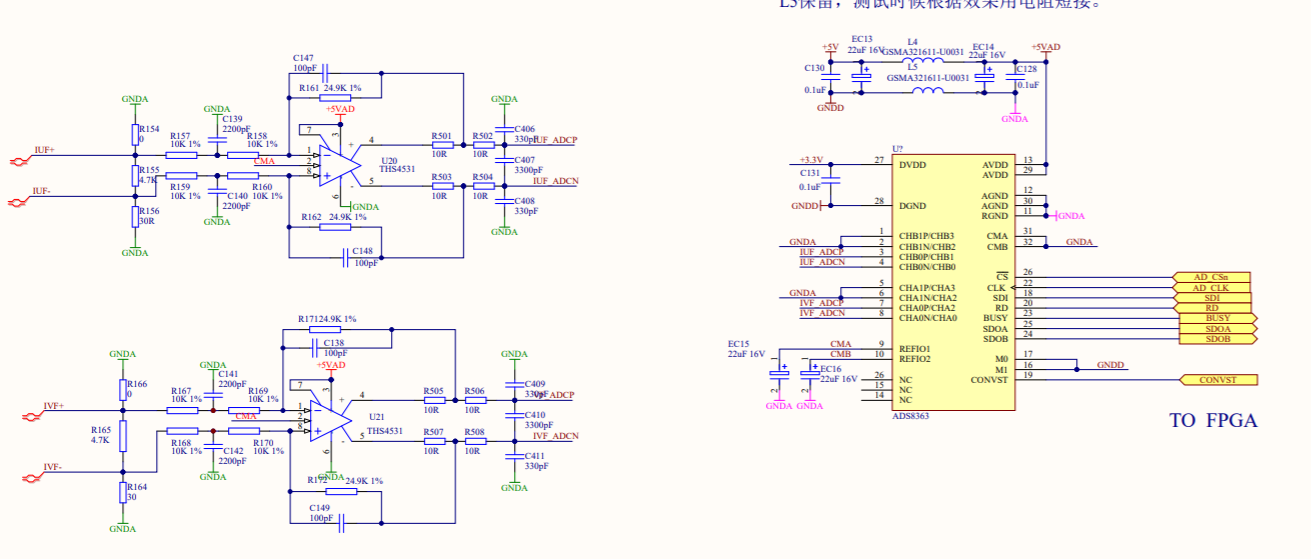

This is my customer design. Could you pls help give any comments? Below are what I found,

1. Leave CMA/CMB pins open, as it is as full differential input use case;

2. Demount R154 R155 R156 C139 C140 C147 C148 C406 C408;

3. For a 16bits application, choose THS4561 with smaller offset;

4. The input signal to FDA is 2.5V common voltage with +-2V swing. Gain is 1.25V/V to differential +-2.5V output swing to ADS8363. I would like to set OCM of THS4531 as 2.5Vref of ADS8363. FDA can be powered by 5V single supply.

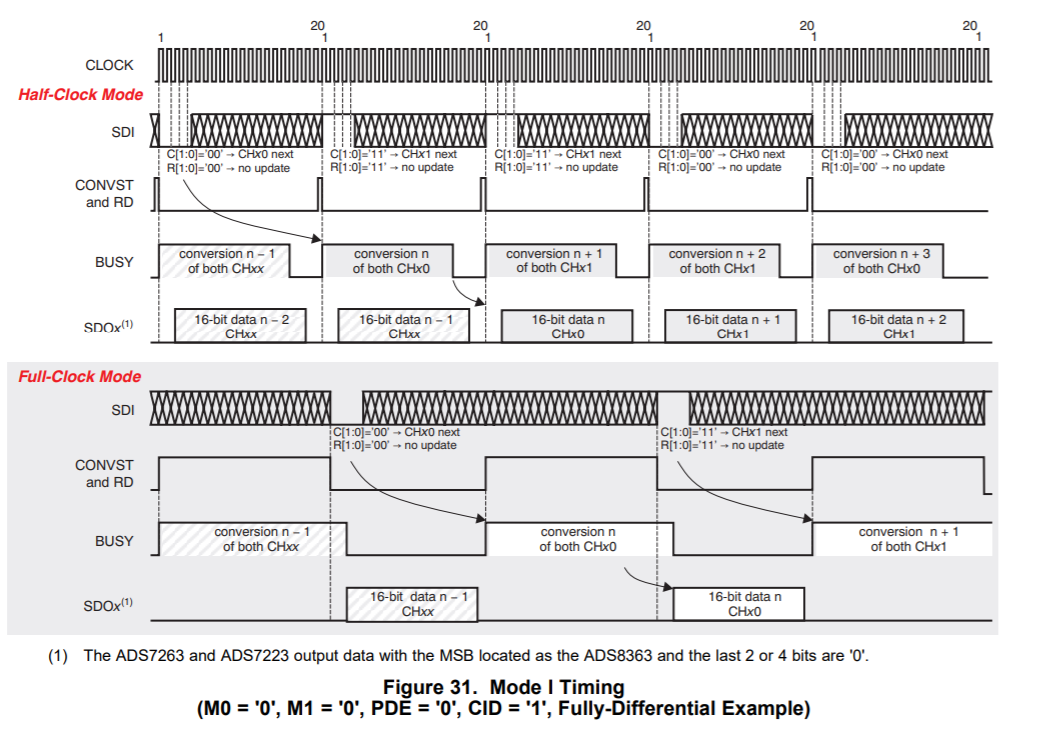

This is a two channel simultaneous sampling. Can I use REFIO1 to supply both ADCs and OCMs of amplifier? I think the buffered REFIO1 can do this and single reference introduces higher accuracy.

BTW, I didn't find the ENOB data in datasheet.

Thanks.