Other Parts Discussed in Thread: DAC80004

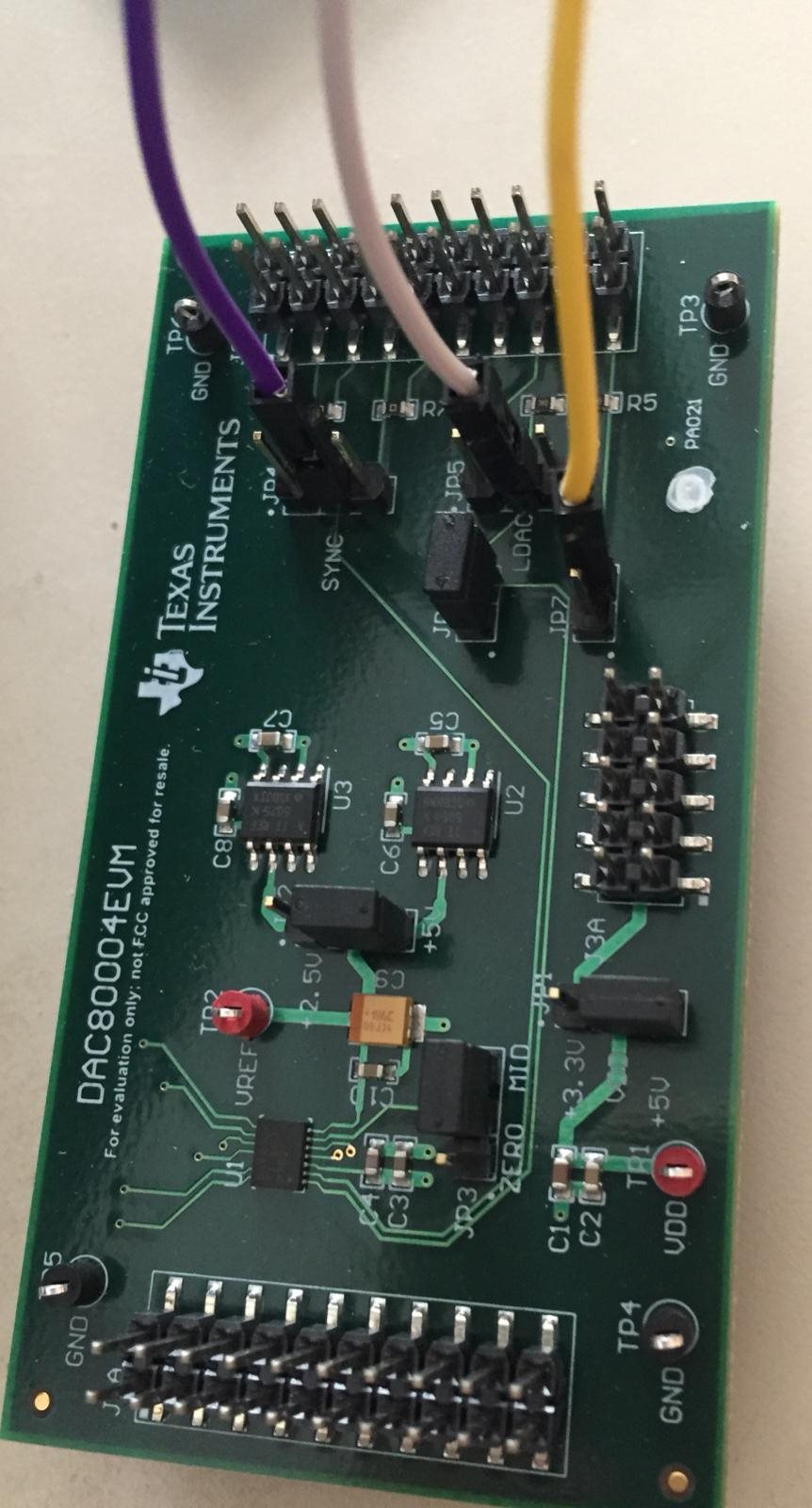

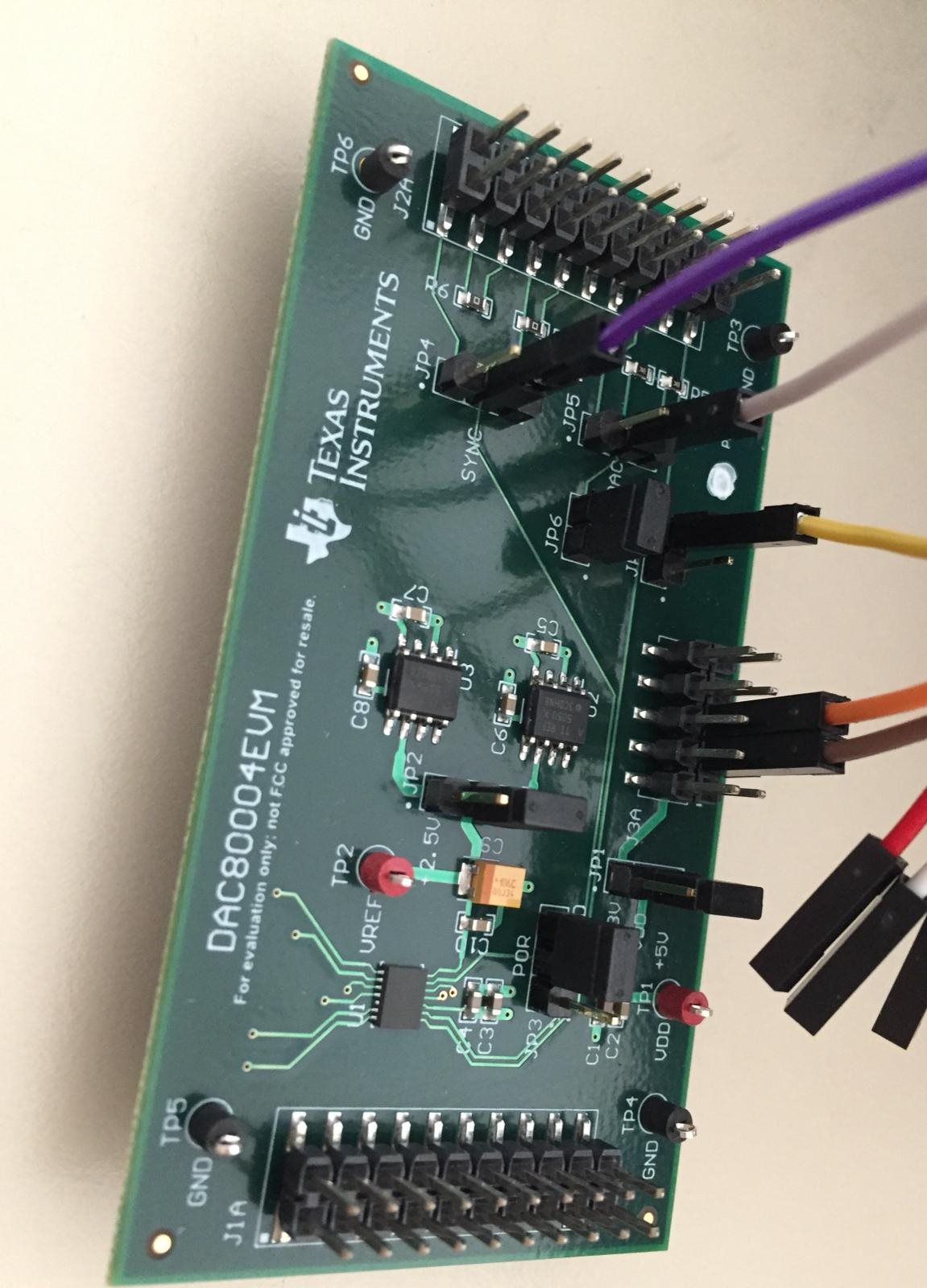

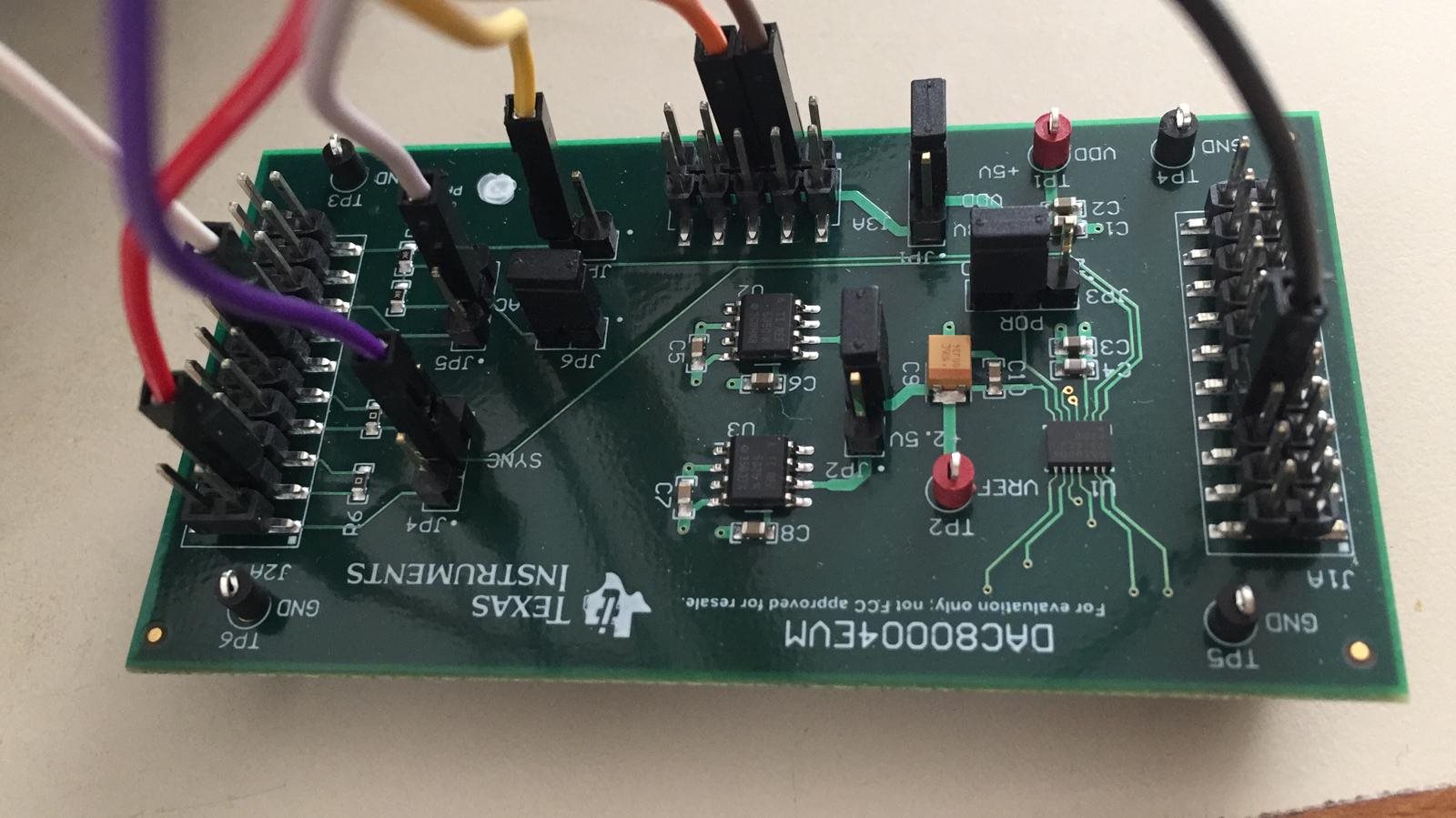

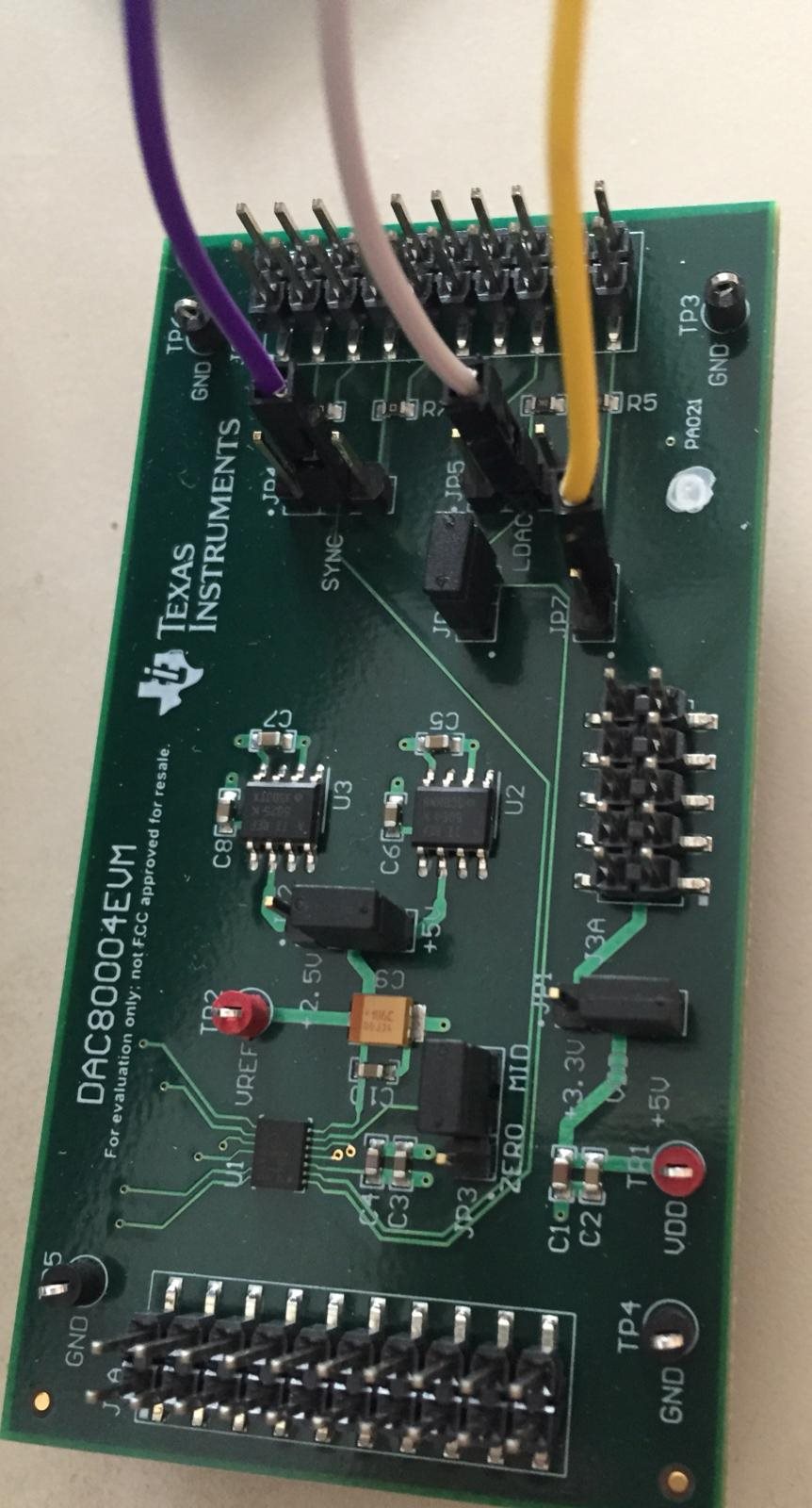

Hello, I have bought DAC80004EVM shown bellow.

I want to program it using Jlink debugger with pin out shown bellow in the poto bellow on the left.

Where do connect the Jlink pins on the DAC80004 board?

Also regarding the Vtref pin,i need add a voltage source to the board an connect Vtref to it?

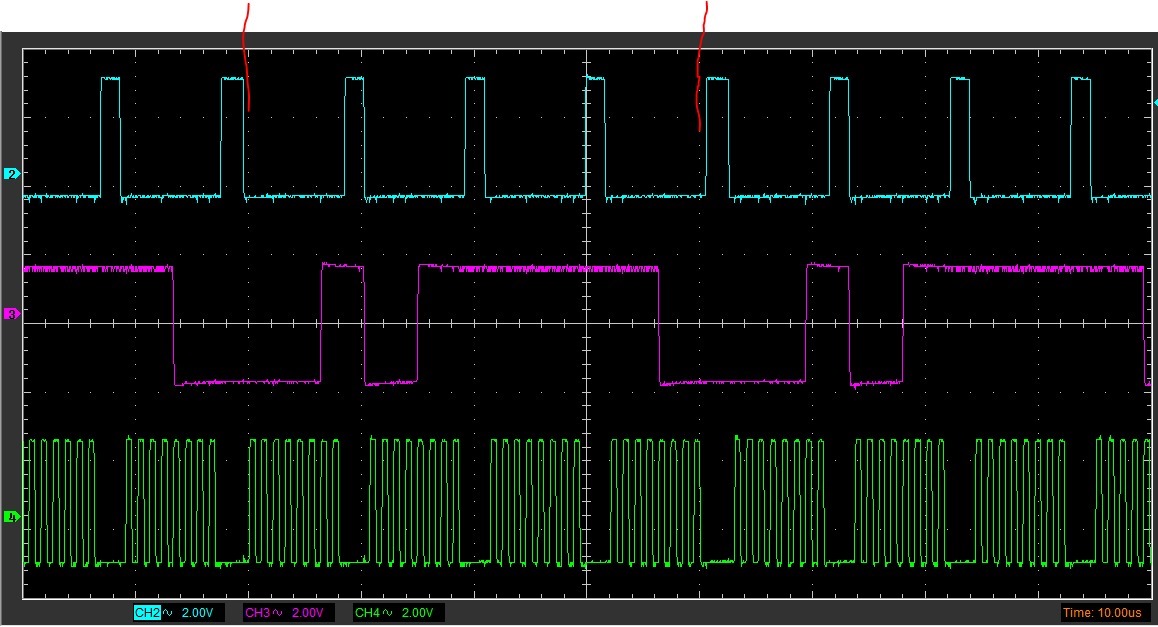

I have programmed DAC80004 before ,the chip was on board ,I connected to the board using JLINK SWD connection, and i communicated with the device using SPI commands.

I want to connect to DAC80004EVM with my JLINK EDU and communicate with it using SPI

Thanks.