Other Parts Discussed in Thread: LMK04828

Hi,

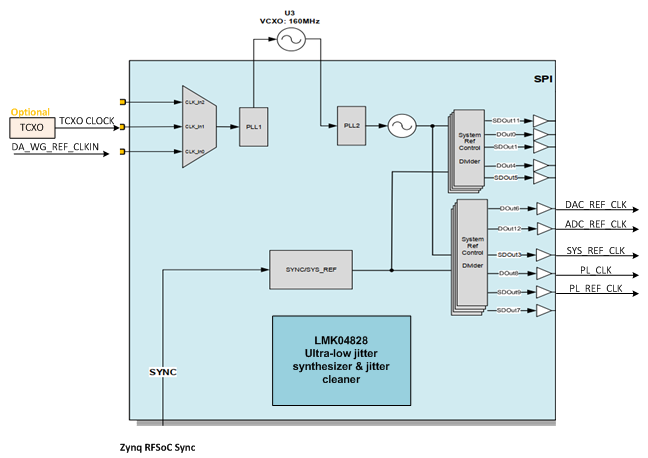

We need to Synchronize two ADC12DJ5200. The sampling clock of both the devices is being generated by a single PLL and both the clock trace lengths are matched on board. We are using the device LMK04828 to generate the device and SYSREF clocks required for JESD204B. The SYSREF trace lengths from LMK to ADC are also matched. The Device clock and SYREF pairs to the FPGA are also length matched. We are operating the ADC in JMODE 20 with a sampling rate of 5.2Gsps

With this, the phase of the data captured between the two ADCs is varying at every power cycle. Please clarify at what stage of the Initialization Setup(Section 8.3) should The Automatic SYSREF Calibration mentioned in Section 7.3.6.3.2 of the datasheet be done.

Regards,

Ayesha