Dear colleagues

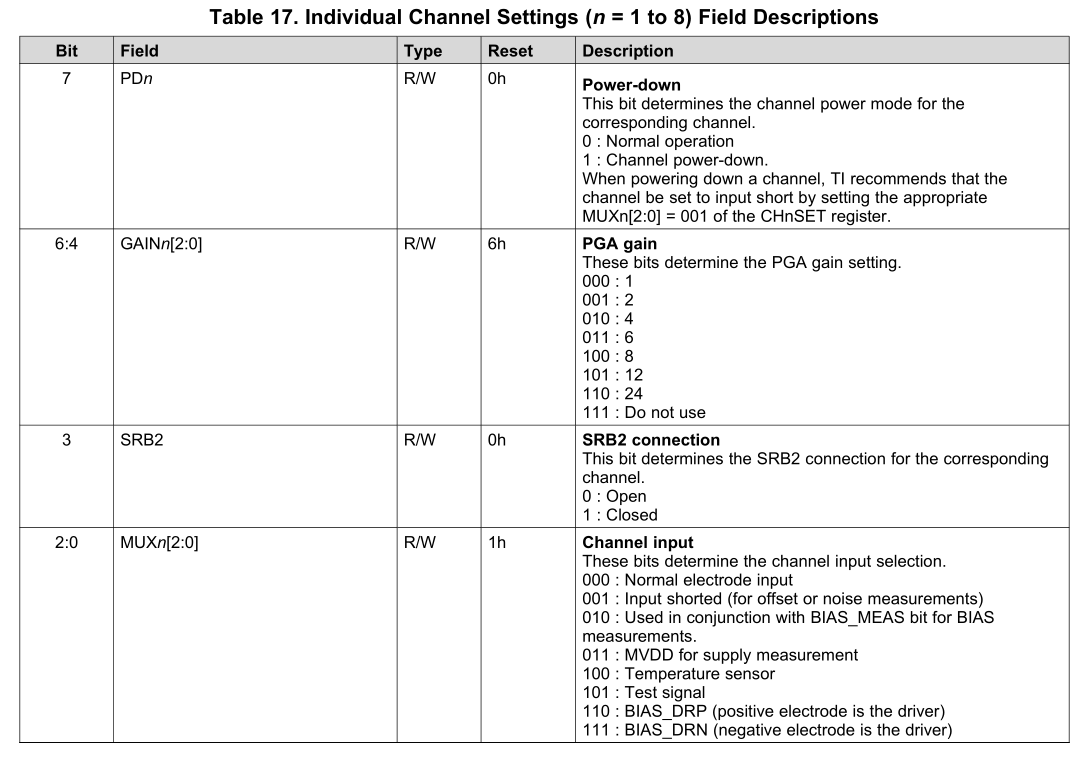

I have a problem with ADS1299.

I've implemented a portable 20-channel EEG device with three ADS1299 and STM32F407 microcontroller (MCU).

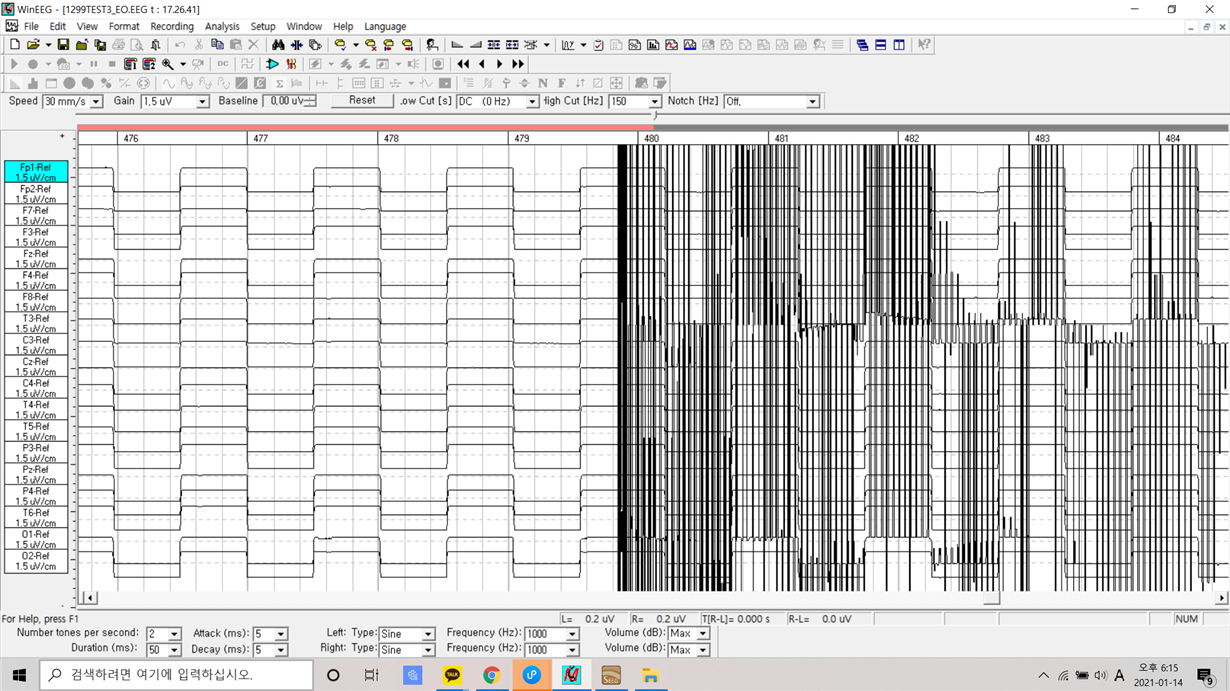

During operation test with a test-signal mode, we found that several channels were severely distorted due to unknown reasons.

Please see the attached picture.

At first, the square waves from each channel were normal, but several channels were distorted.

(Test signals are overlapped, but several signals are normal)

The software engineer said that he inspected the data during SPI communication between the ADS1299 and MCU using STM Studio.

He said that the original test signals were distorted in ADS1299 and they were transmitted to the MCU.

My questions are....

1) Is it possible that the square test signals can be distorted due to several reasons, for example, an electronic circuit or test conditions?

2) If then, how can we fix this problem?

I will wait your useful advice

Thank you in advance

Best regards

Heejin Kim