Other Parts Discussed in Thread: TINA-TI, DAC8311

Hi,

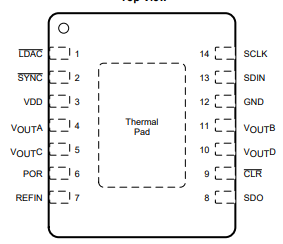

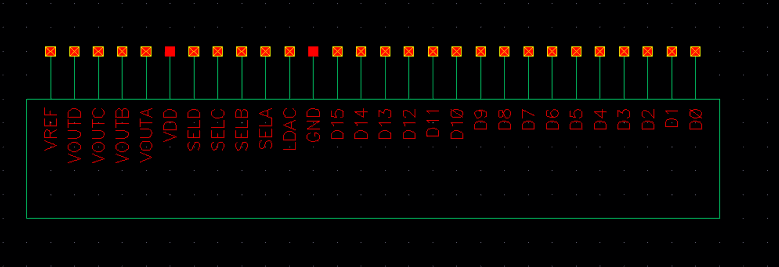

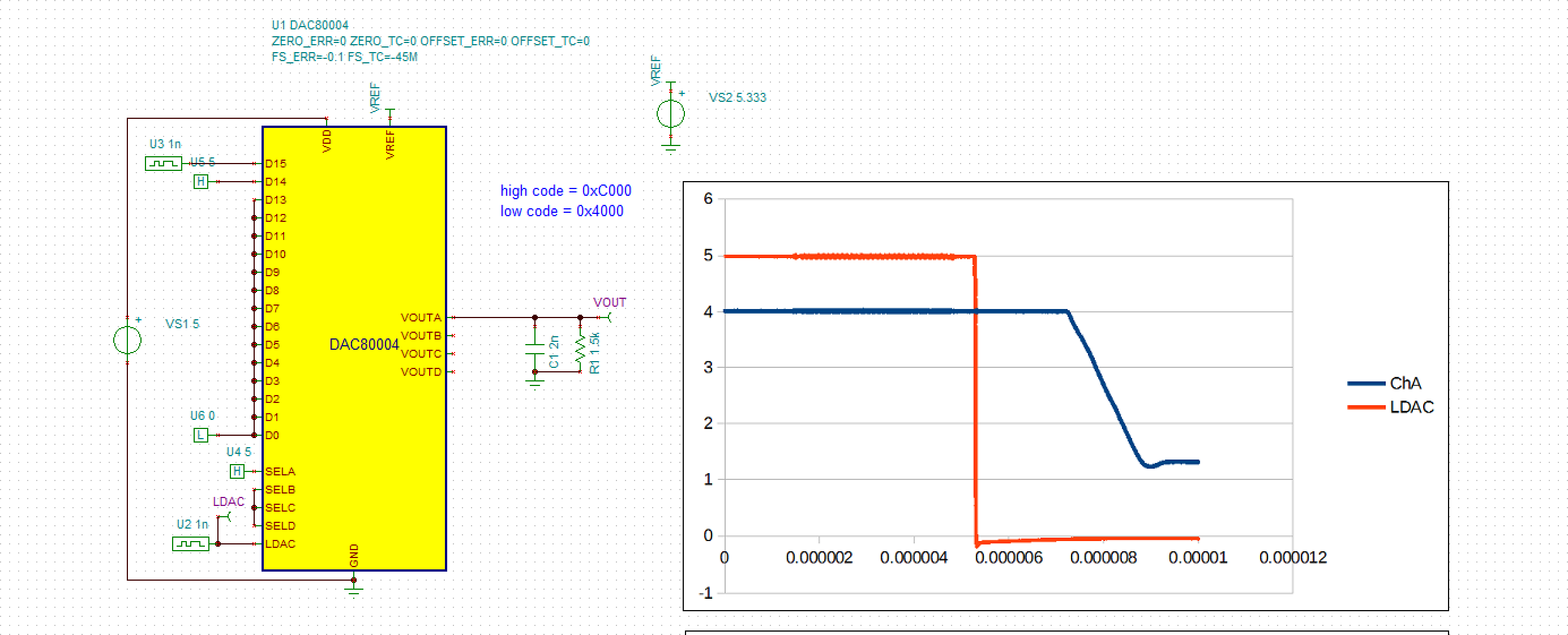

I need the spice model(.CIR file) for DAC80004IPW. The one which is available on ti.com is the encrypted model. I need the unencrypted one, as i want to create a symbol for this component and then use it in a test bench.