Hi,

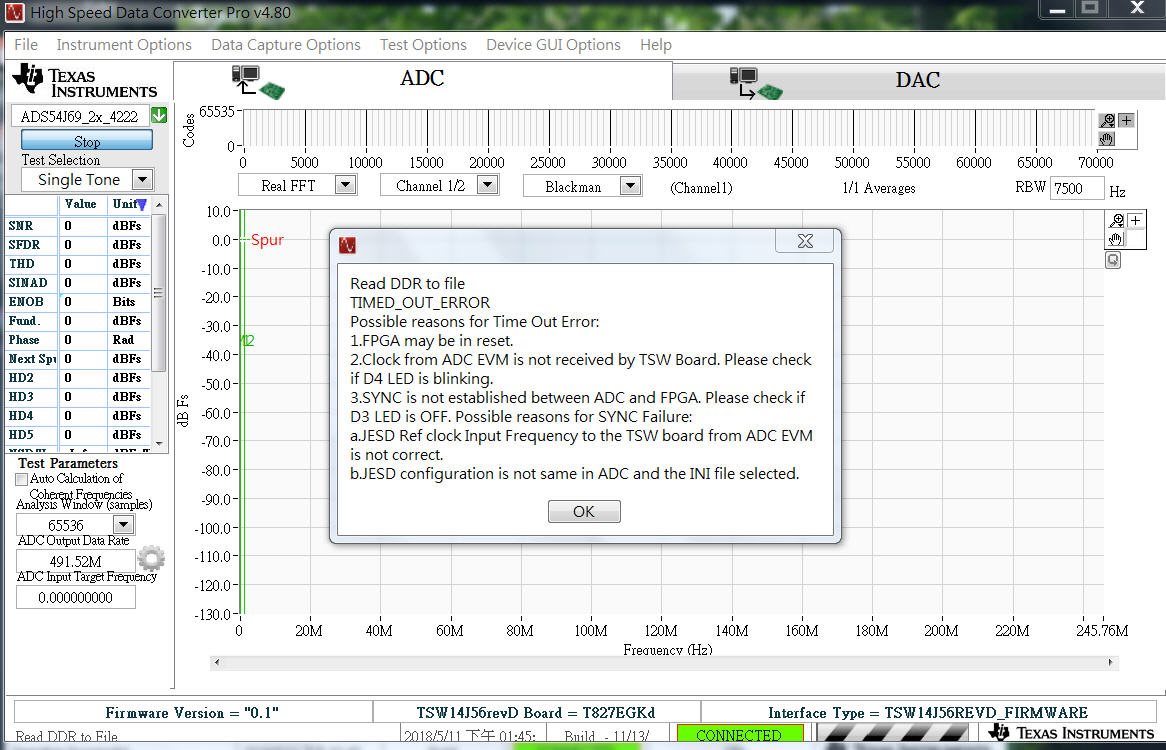

I got errors about "Read DDR to file" in HSDC pro software. The error message shows "Timed_OUT_ERROR".

My hardware are: Adc board is ads54j69 & Fpga board is tsw14j56.

My HSDC pro setting are:

The sampling frequency is 491.52MHz, Sample point is 65536

the function generator is set 10MHZ, Ro=50ohm, amp=0.3vpp, bias=0.15v.

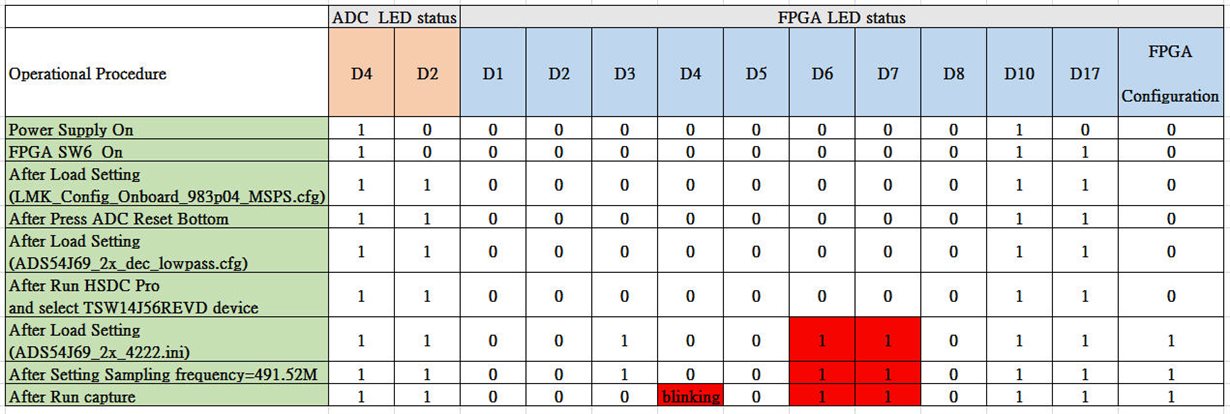

I had checked led status in fpga board in which D4 led is blinking, D3 led is off. and ADC PLL2 lock (D2 led is on).

The setting file of the Adc board are LMK_Config_Onboard_983p04_MSPS and ADS54J69_2x_dec_lowpass.

How can i solve this timed out error? this problem confuses me about one week.

Many thanks for the help.