Hi team

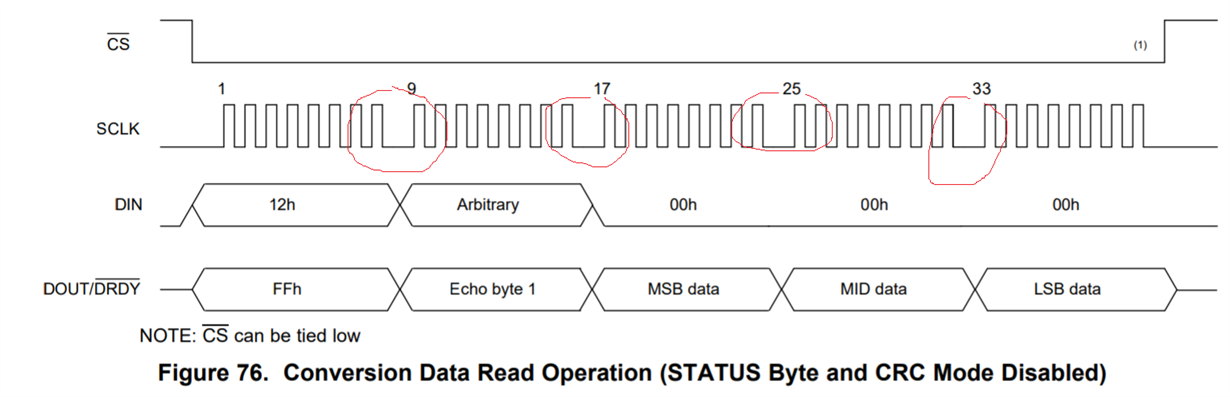

Looking at figure 76&77 on the datasheet, it seems that the time of SCLKs between 8bit and 9bit, 16bit and 17bit and so on is longer than others.

How should we understand the longer time? Are there any requirements for the SCLK?

Regards,

Noriyuki Takahashi