Application:

Design: DAC80501ZDGSR, VDD = 3.3V, I2C Mode, A0 tie to SCL, use Internal REF

REF-ALARM bit of Reg 0x07 always set at power up and Vout = 0 (regardless of value load into Reg 0x08)

On Power up, this are the Registers reading:

DEVID -> 0x0115

SYNC -> 0x0100

CONFIG -> 0x0200

GAIN -> 0x0001

TRIGGER -> 0x0000

STATUS -> 0001

DAC -> 0x0000

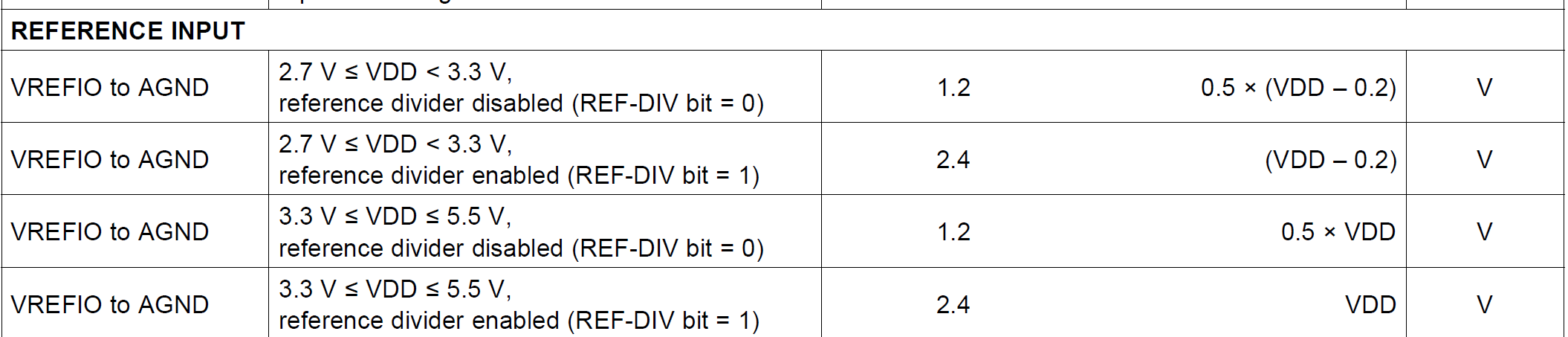

VREF IO pin measured 2.5V.

So far, the only way to clear the REF-ALARM bit is to either Set the REF_PWDWN bit or set the DAC_PWDWN bit in the CONFIG Register.

1) Bit 9 of CONFIG always set, is that OK?

2) What else could be wrong, bad chip?

******************************************************************

REF-ALARM bit. Reads 1 when the difference between the

reference and supply pins is below a minimum analog threshold.

Reads 0 otherwise.

3) What is this minimum analog Threshold value?