Hi TI,

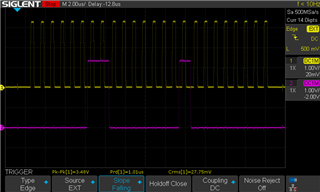

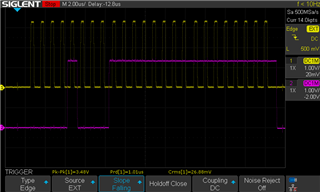

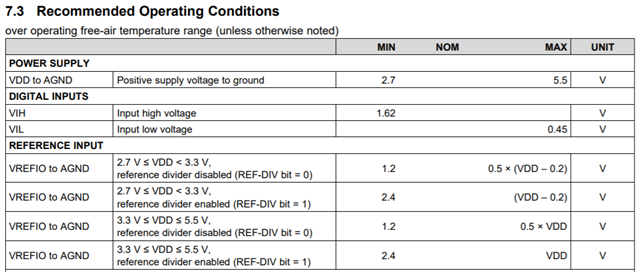

Our new design uses a DAC80501, and we would prefer to operate it with output from 0-5V on SPI. However, when powering it with a regulated 5V supply (confirmed stable with an oscilloscope), we are unable to communicate with it (no commands seem to have any effect; these commands are sent on 3.3V). Switching the DAC's power (VDD) to 3.3V with no other changes to the system makes everything operate as we expect; we can control the DAC output voltage via SPI. Do you have any idea why operating at 5V would give us issues while 3.3V works fine? While we can supply VDD with 3.3V, we'd prefer to operate at 5V. I've also included a snapshot of the relevant part of the circuit, in case it's helpful.

Thank you in advance for any advice you can give us!

Cheers,

Dan