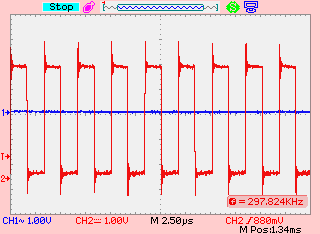

1. WCLK changes on the falling edge of BCLK

2. Data MSB is delayed one bit after WCLK’s start.

1. DAC_fs: 44.1K

2. Word length: 16 bit

register setting said:uint8_t dac_data;//page 0AIC3106_writeRegister(0x00, 0x00);//page 0AIC3106_writeRegister(0x01, 0x01);//? p46: Initiate SW reset (PLL is powered off as part of reset)AIC3106_readRegister(0x36, &dac_data);dac_data &= ~0x06;dac_data |= 0x02;AIC3106_writeRegister(0x36, dac_data);//enable DIN, though not necessary since it is by default enabledAIC3106_writeRegister(0x1b, 0x3c);//I2S, both BCLK and WCLK outputAIC3106_writeRegister(0x04, 0x03);//Clock-Gen Muxing: MCLK -> PLL, PLL -> CODECAIC3106_writeRegister(0x06, 0x07);//J=7AIC3106_writeRegister(0x07, 0x02);//D MSB 512AIC3106_writeRegister(0x08, 0x30);//D LSB 48AIC3106_writeRegister(0x05, 0x91);//PLL on, P=R=1USTIMER_delay(12000); //delay 12ms > 10msAIC3106_writeRegister(0x0b, 0x85);//NDAC on, 5AIC3106_writeRegister(0x0c, 0x83);//MDAC on, 3AIC3106_writeRegister(0x0d, 0x00);//DOSR MSB 0AIC3106_writeRegister(0x0e, 0x80);//DOSR LSB 128AIC3106_writeRegister(0x3f, 0xd4);//Left & right DAC on, and select data pathAIC3106_writeRegister(0x40, 0x00);//left & right DAC not mutedAIC3106_writeRegister(0x3c, 0x0b);//PRB_P11, stereoAIC3106_writeRegister(0x1d, /*0x05*/0x01);//BCLK and WCLK Active Even With Codec Powered Down//BDIV_CLKIN = DAC_MOD_CLK = DOSR * DAC_fsAIC3106_writeRegister(0x1e, 0x84);//Divider on, /4//page 1AIC3106_writeRegister(0x00, 0x01);//page 1AIC3106_writeRegister(0x20, 0x86);//Class-D output driver is powered upAIC3106_writeRegister(0x2a, 0x05);//Class-D driver is not muted.AIC3106_writeRegister(0x23, 0x44);//DAC_L is routed to the left-channel mixer amplifier//DAC_R is routed to the right-channel mixer amplifier