Other Parts Discussed in Thread: DAC3484, DAC3482

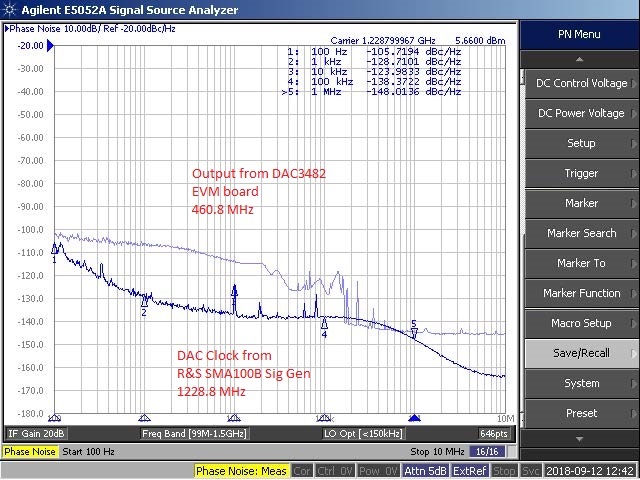

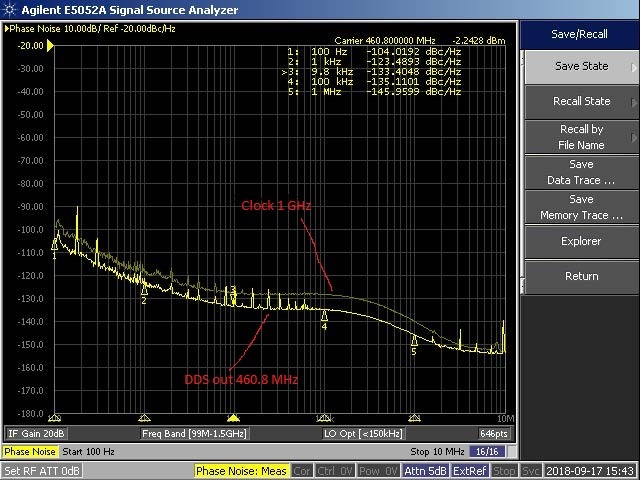

I am using the DAC 3482 as a DDS using the NCO in the part. My clock frequency is 1228.8 MHz and I'm generating a signal at 3/8 of Fc (460.8 MHz).

As can be seen from the picture below the phase out of the DAC is higher then that of the clock. I would expect the DAC to be approximately 8dB lower or at the noise floor of the part which looks to be about -145 dBc/Hz. The results are the same when we input the clock from the LMX chip or bypass it and feed the clock to the DAC directly from the signal generator.

Any help you can provide would be welcome.