Hi Jim,

I have successfully exported data sourced from JESD block from the DAC since I used the order that you gave me.

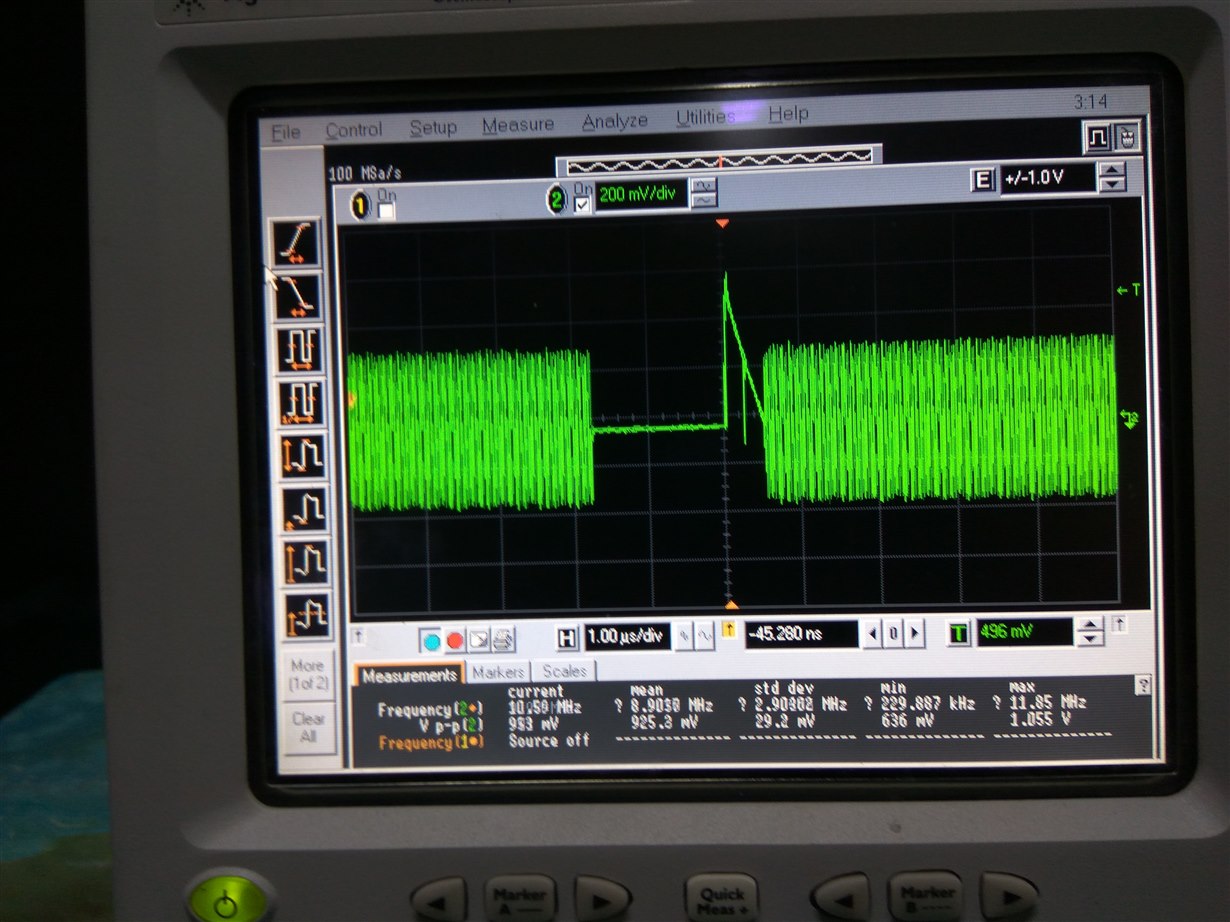

But there is still a problem. The signal SYNCB outputted from the DAC38J84 will become low every other time. And then the synchronization will start over again. So is there any possible that some of my registers are not configured correctly?

Attached is my configuration. And the two pictures are 10MHz sine wave signal outputted from DAC captured by the oscilloscope, and the data outputted from the JESD IP core connected to DAC38J84 observed by ILA of VIVADO.