Hi,

I wrote the code as specified in the ADS130E08 datasheet flowchart (pg45).

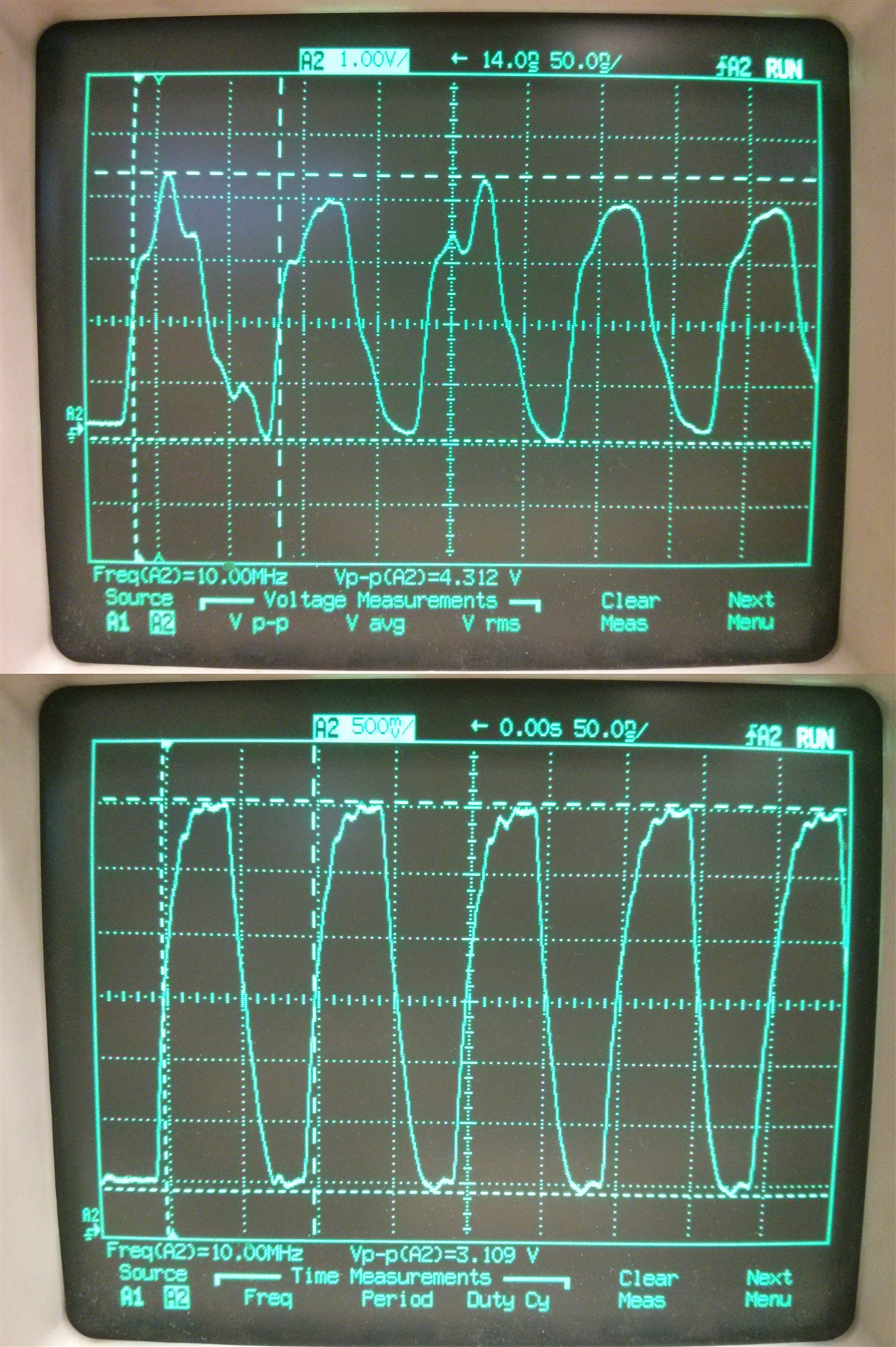

I've attached some logic analyzer pictures and I'd like some validation as to whether it is working correctly.

Logic Analyzer pictures based on Initial Flowchart:

1) Reset Pulse -> SDATAC -> WREG config and set channel short -> START -> RDATAC

2) SDATAC -> WREG config square wave test signal -> RDATAC

3) Capture Data and output on terminal

The last picture is my captured signal on the terminal. Received : 57375, 2304, 61951, 62463, 61951, 62463, 62463, 236

Is the received value correct? Anything to improve on (timing, etc)?

Thanks,

Stephen