Hello,

Do you have a power up sequence for the ads1296 for DVDD, AVDD, /RESET, /PWDN and /CS signals please?

I look at the datesheet Power-up sequencing but all signals are not indicated. I am using the internal clock.

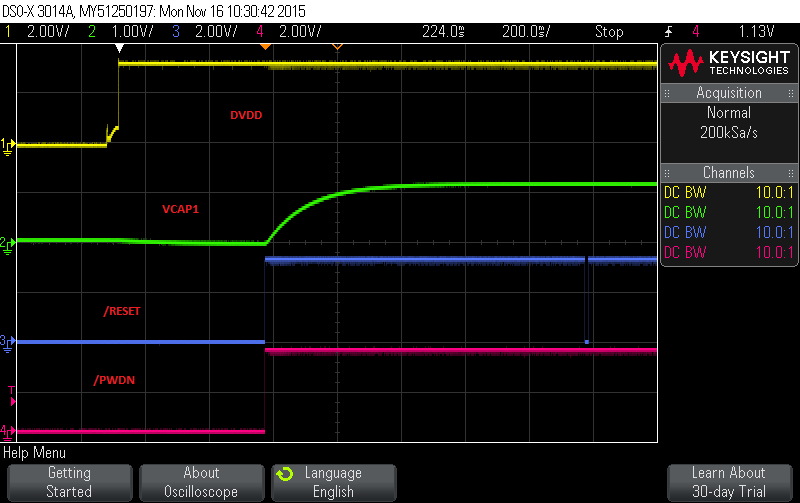

I am do the following sequence and it does not work every time:

- set DVDD and AVDD while other signals are low

- wait 500ms

- set /RESET high

- set /PWDN high

- wait 1000ms (on oscilloscope VCAP1 is at 1.1V after 500ms)

- set /RESET low

- wait 10ms

- set /RESET high

- set /CS high

- wait 500ms

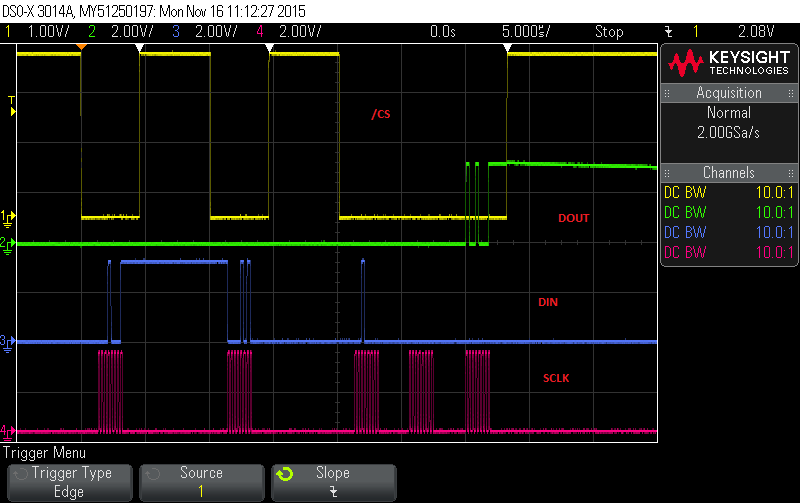

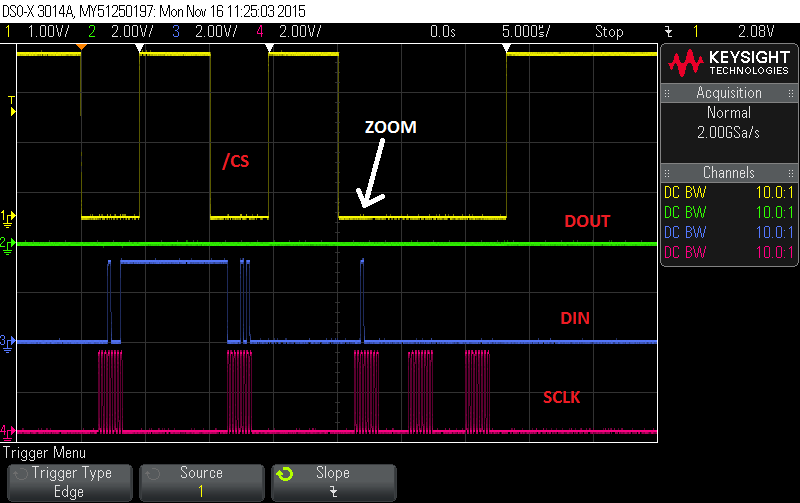

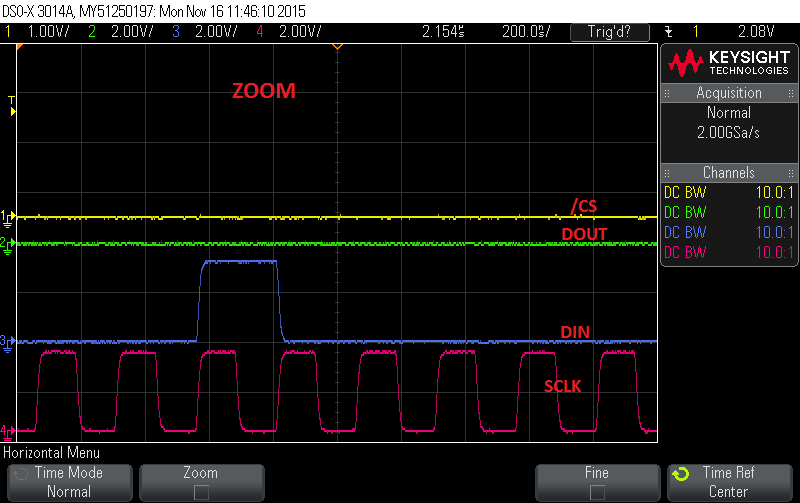

- send spi SDATAC (0x11) command

- wait 20ms

- send spi STOP (0x0A) command

- wait 1500ms

- read ID register to check the value

=> here sometime the return value is 0x00 ????, sometime it is a success at the first attempt ....

After multiples reads it finishes by a success (0x91) but the number of reads before a success is random ????

it could be up to 20 reads before a success ....

Best regards

Mich