Other Parts Discussed in Thread: DAC8760, DAC7750

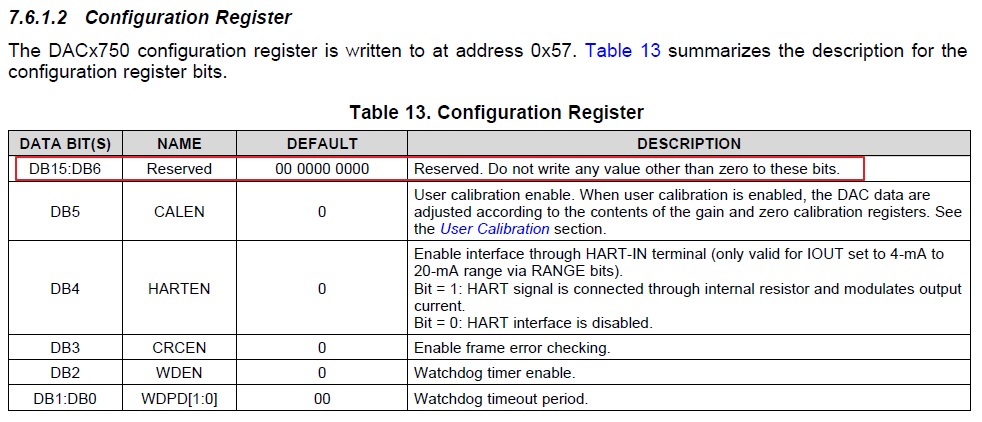

We use two DAC7750 configured in daisy chain mode. They share the SPI bus with an external SPI flash. The problem occurs when the pattern 0x57, 0x58, 0x59 is sent to the external flash (without any rising edge on the LATCH input of the DAC). In this case, the first DAC of the daisy chain stops working correctly as if its configuration register was corrupted. A software reset of the DAC or a reconfiguration of the configuration register seems to bring back the DAC in a normal process. I found an errata pretty similar to this one but with the DAC8760 (See https://e2e.ti.com/support/data_converters/precision_data_converters/f/73/t/403318).

Could someone confirm me that this is the same kind of problem and what the proposed work-around are.

Another question. Is it possible to use two DAC7750 on the same SPI bus but not configured in daisy chain mode? This is not clear in the datasheet. I suspect that the same kind of problem could happen.