Dear Team,

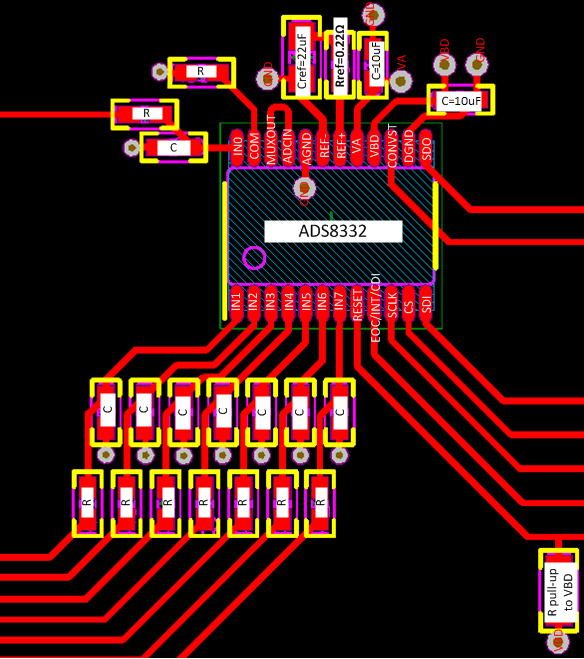

My customer would like to use ADS8332 on their new design. They prefer to use TSSOP package and they need a layout guideline for this package. datasheet and EVM documents have guidelines for only QFN package.

Do you have a guideline for TSSOP package as well?

Best regards,

Caglar