Hello

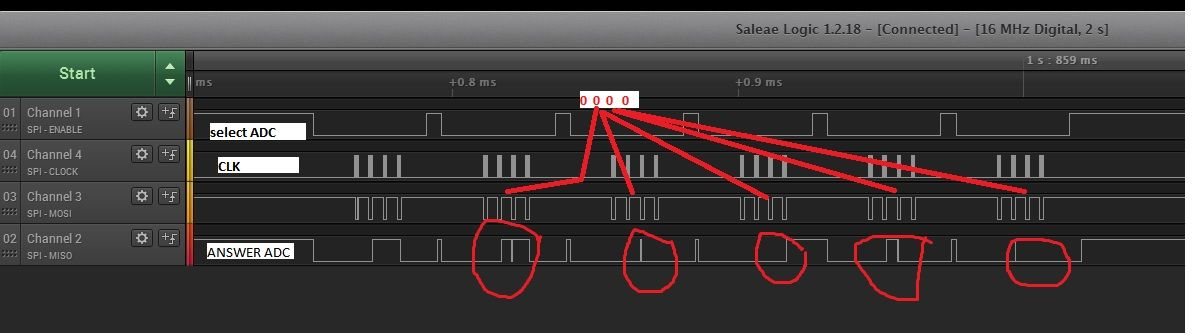

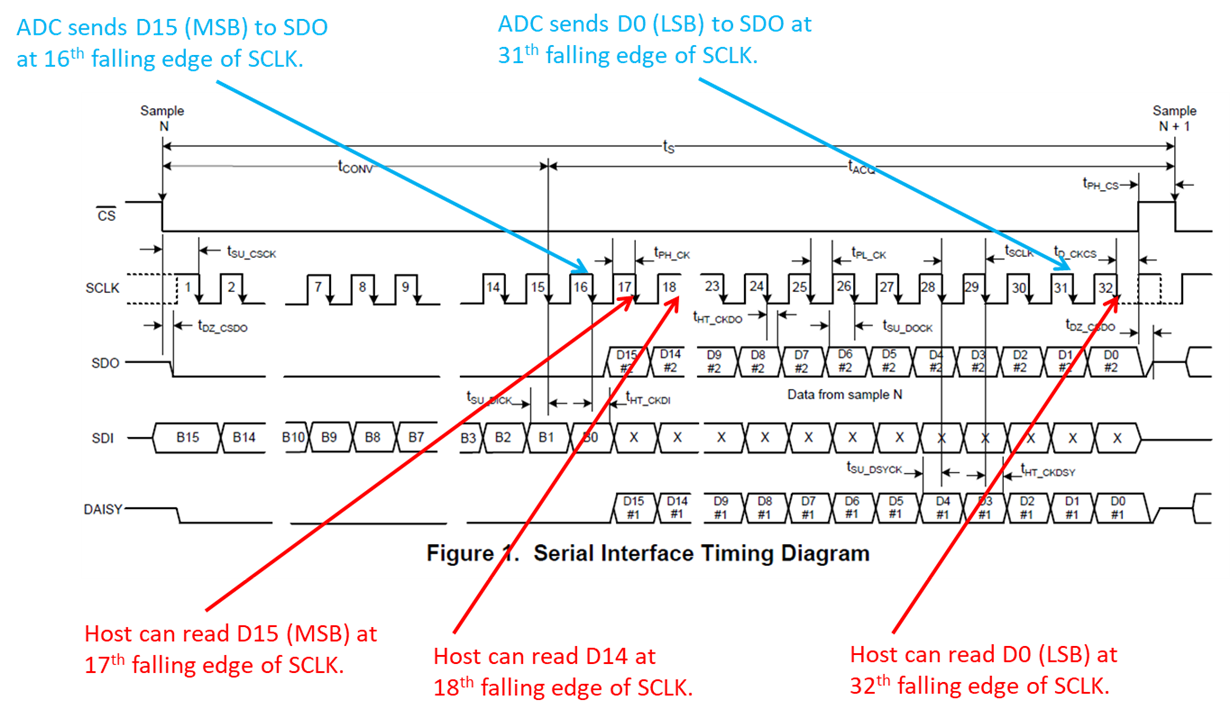

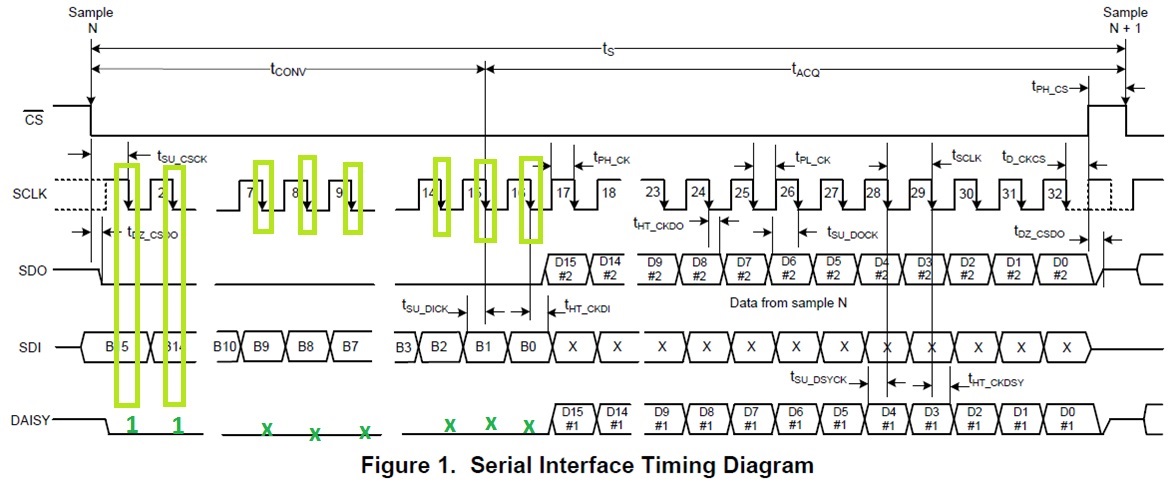

ADS8684 on all channels, SPI gives random numbers, help me.

Records in the registers are not what they did.

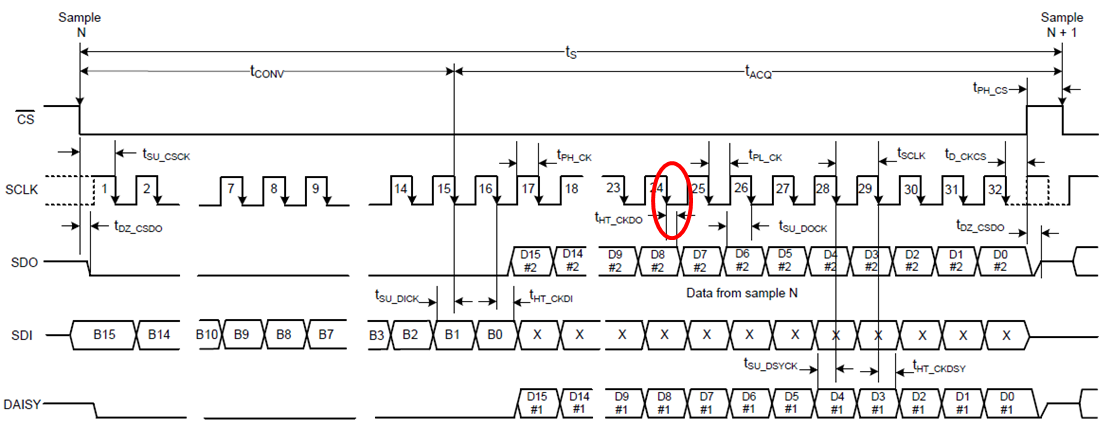

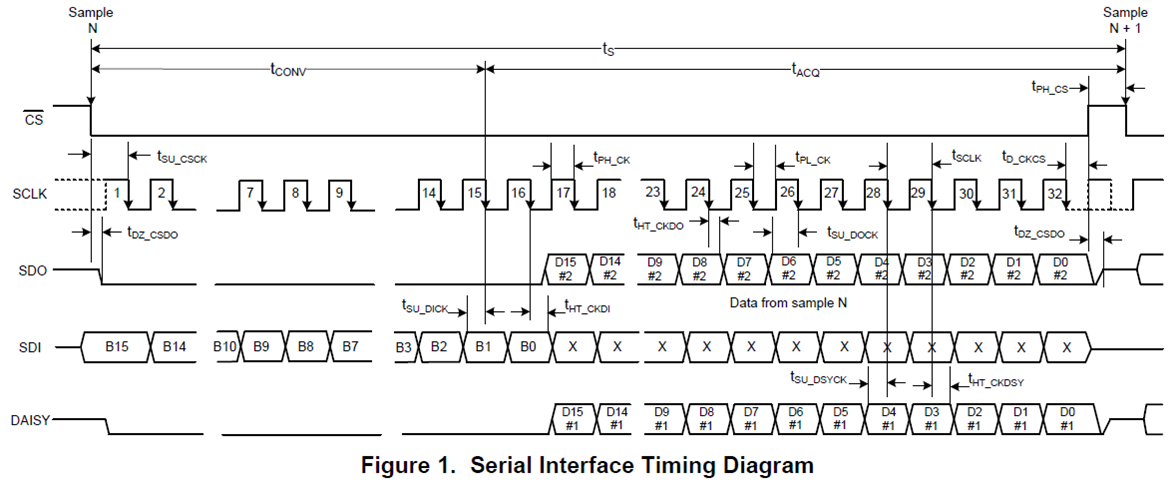

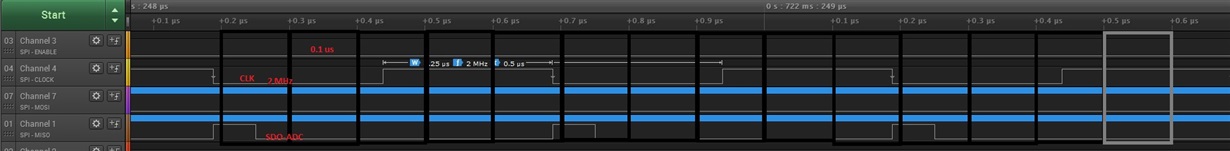

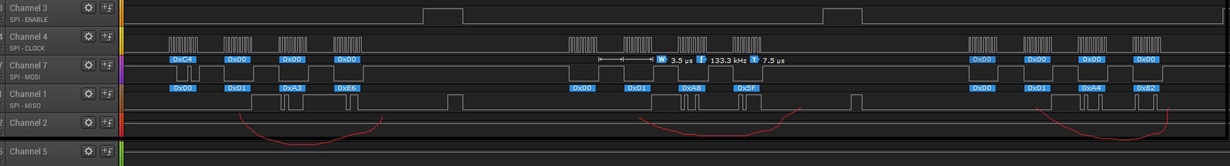

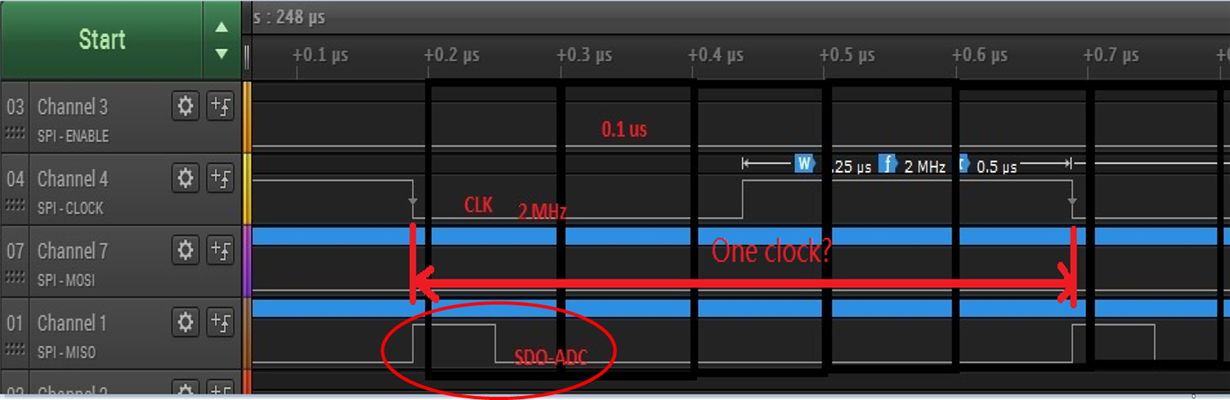

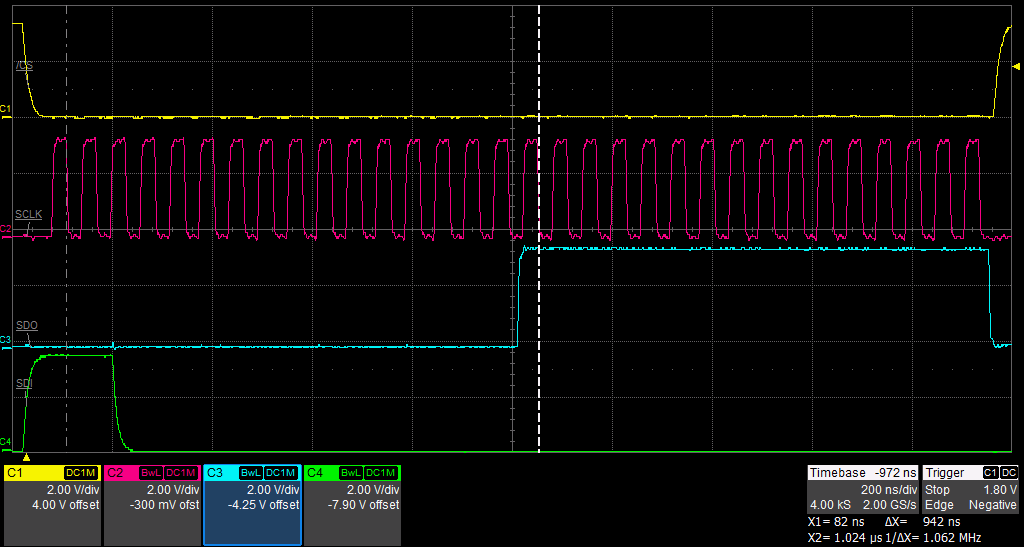

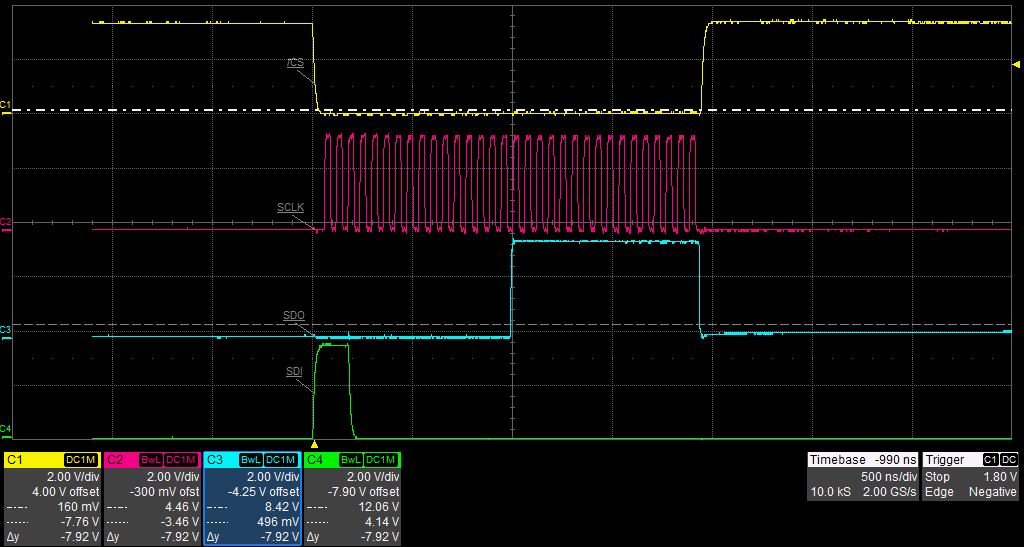

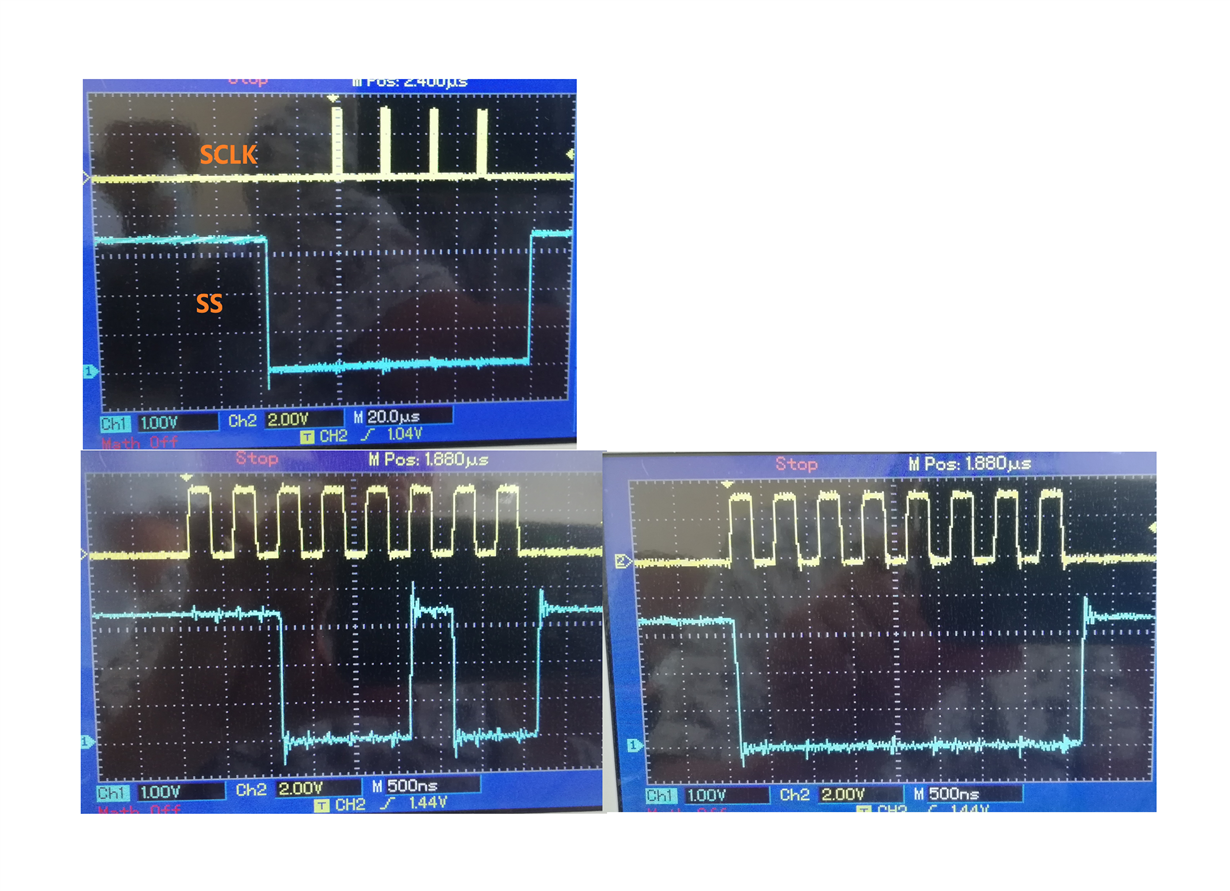

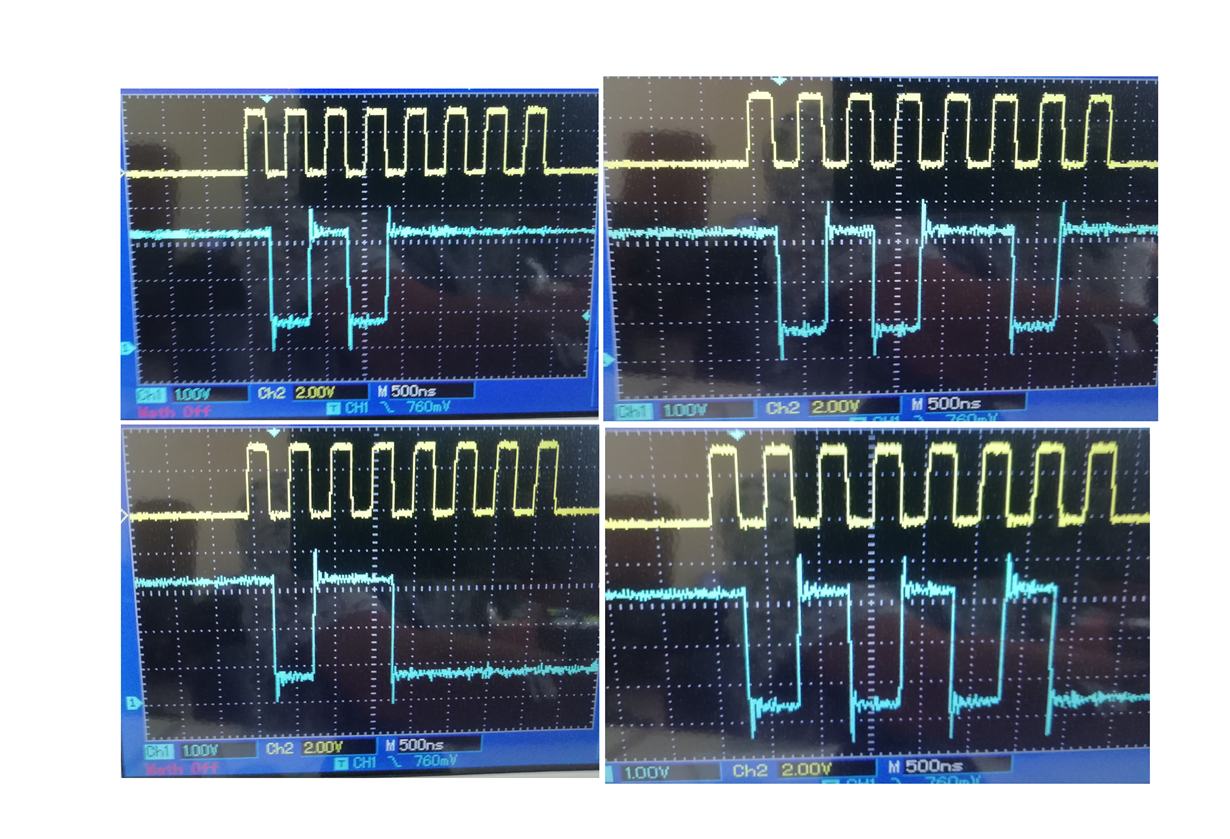

SPI is set to the falling edge, the frequency is 300 kHz

code sample

uint_8t b1, b2, b3, b4;

SELECT_ADC; // low level output 38

SPI_SENDBYTE_ADC (0xC0); // 1 channel - 0xC0 2 channel - 0xC4

SPI_SENDBYTE_ADC (0x00);

SPI_SENDBYTE_ADC (0x00);

SPI_SENDBYTE_ADC (0x00);

UNSELECT_ADC; // high level output 38

delay_us (1);

SELECT_ADC;

SPI_SENDBYTE_ADC (0x00); // command NoOp

SPI_SENDBYTE_ADC (0x00);

b1 = SPI_SENDBYTE_ADC (0x00);

b2 = SPI_SENDBYTE_ADC (0x00);

UNSELECT_ADC;

delay_us (1);

SELECT_ADC;

SPI_SENDBYTE_ADC (0x00); // command NoOp

SPI_SENDBYTE_ADC (0x00);

b3 = SPI_SENDBYTE_ADC (0x00); // get the data

b4 = SPI_SENDBYTE_ADC (0x00); // get the data

UNSELECT_ADC;

The values in b1, b2, b3, b4 are random examples 0, 255, 1, 127, 254, 128

I checked the voltage at the pins of the chip

The voltage on channel 1 and 2 pin16,18 checked the supplied constant of 0.6V

pin 5 - 4.08 V

pin 7 - 4.12 V

pins 9,30 - 5.01V

pins 2,34 - 3.3 V

pins 3,4,6,8,31,32,33, 28,29,17,19,20,22 connected to the ground