Hello

I am using ADS8339 in 3 wire mode at 240ksps conversion rate with Vref 2.5 Volts, with 5MHz SPI clock for data out.

Problem : I am not able to obtain all the bits from ADC for 0 volts first 11 bits of MSB are 1's and rest 5 are zero.

As I reduce the SPI clock to 1MHz. I able to get correct data from but (15-bits only).

As soon as I go above that in integer multiples of 1MHz rate It starts loosing LSBs.

Question :

1. I am not sure why this is happening. Not sure Why am I not able to get 16 bits, Please help.

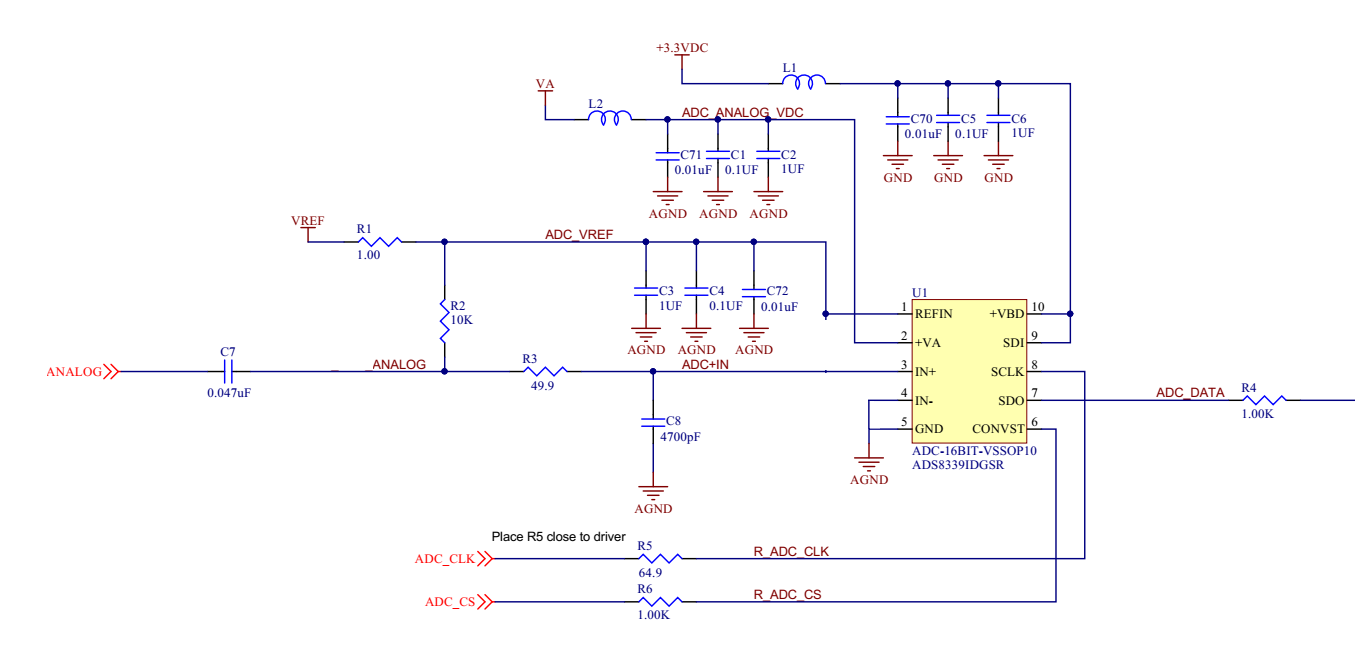

Here's the schematic if that helps.

Thanks,

Rahul