We are getting data out of this chip, but there seems to be issues with the data. Mostly, the last three bits coming out are nearly all 100, effectively reducing the 16-bit resolution to 13-bit. Before we go to the trouble of reconfiguring the system, I wanted to know if any of the following creates any known issues, or if it should work OK in this manner.

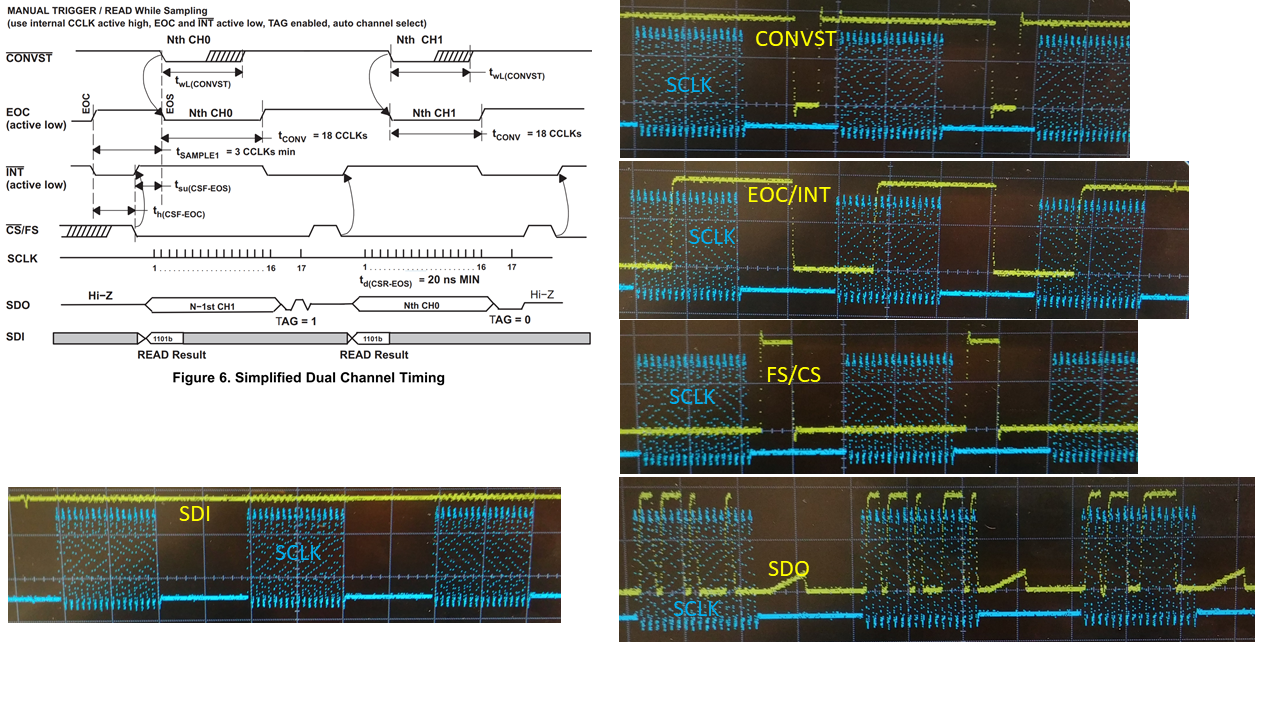

For TAG use, I would like to know if the 17 SCLK pulses can simply be all spaced at the same interval or if there needs to be a space between the 16th and 17th pulse. The datasheet Figures (such as Figure 6) show 16 pulses on SCLK, a small space, then the 17th pulse, but this small space is not documented anywhere that I can find.

Also, one of our engineers configured the SDI signal to remain essentially always high, there is no 1101 that coincides with the first 4 pulses of the SCLK pulse stream. Does this create a problem? Or does the SDI pin really need the 1101 to properly function? The SDI only has a zero for an occasional reset, but during data read-out, the SDI signal is always high. This seems to conflict with the datasheet showing a 1101 is needed, but the engineer that configured it this way is claiming that since we are getting data out, it should be fine. I'm wondering if this could be affecting the timing, however, and maybe contributing to our strange issue of nearly all data ending in 100.

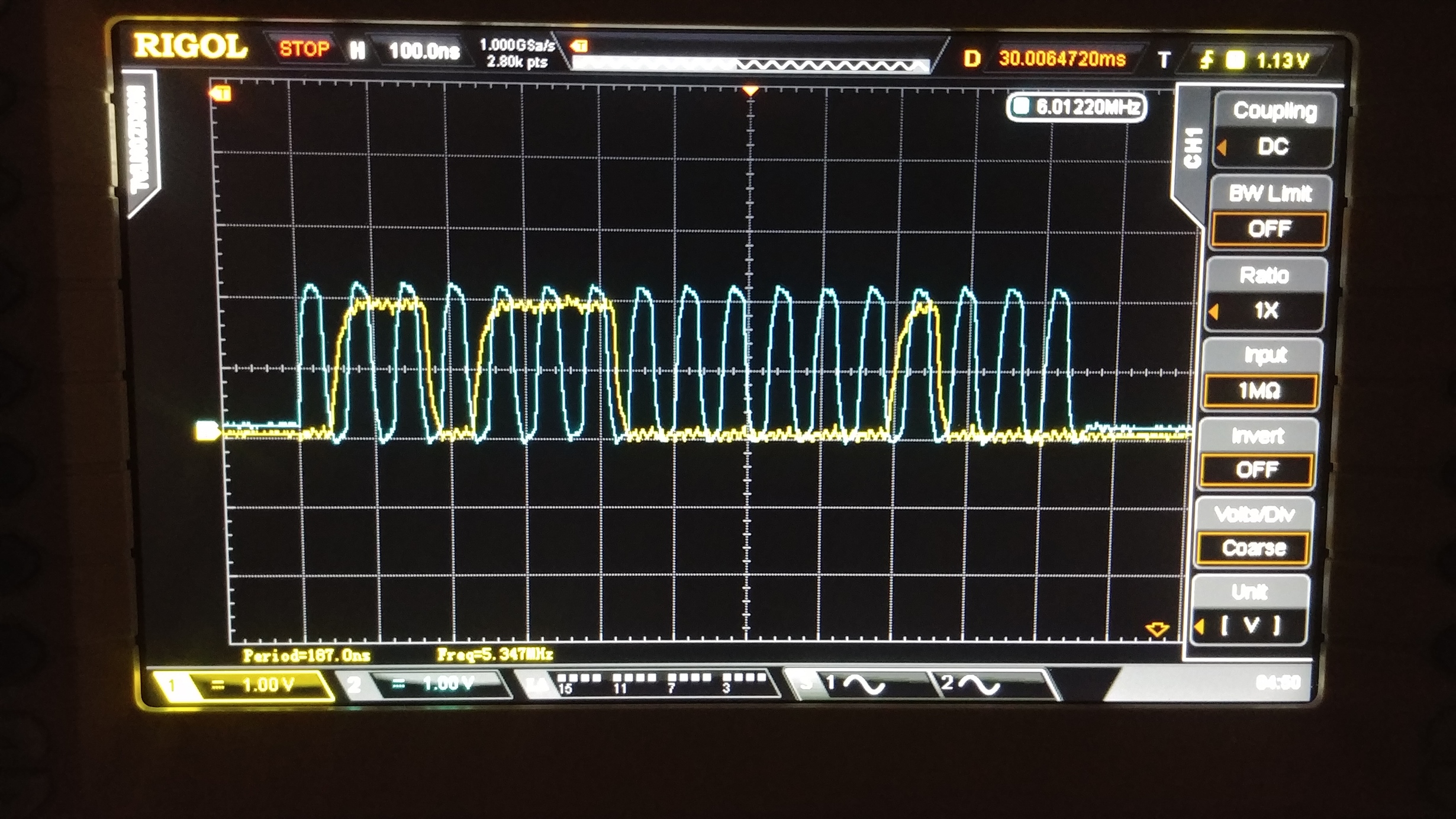

One other strange thing we see is what appears to be a data anomaly when the 15th and 16th bits flip (right at the mid-point). Our data seems stretched in this region - sinusoids for example show elongation near this value, and I'm wondering if the above issues may also be causing this. The elongation is on the order of 3-bits (8 counts). It's very obvious if for example the tip of a sinusoid barely crosses the midpoint.