Os Version: Linux Ubuntu 10.4 LTE 32 Bit

Uname -a : 2.6.32-46-generic #108-Ubuntu SMP Thu Apr 11 15:55:01 UTC 2013 i686 GNU/Linux

CCS Version: 5.4.0.00091

Licence: limited version both MSP and ARM (buy full licence planned later if all processor specific issue (HW, SW and not least availability get solved)

Trouble is version independent, for now I am using 32BIt OS, I Also installed on my next laptop but on latest 64Bit Ubuntu refuse to start.. (I fix myself later lib dependence)

I am porting examples from LM3S to get acquainted to LM4/TIVA, this migration is not pain free, I resolved the stack failure but this also suffer a so strange problem I am not able to address from where it come, deterministic execute first time but not the second one identical instruction, problem is repetitive to same assembly instruction forever.

The driver module code execute right on SdCard example ported to this platform but not this reduced 2555.grlib_demo.zip.

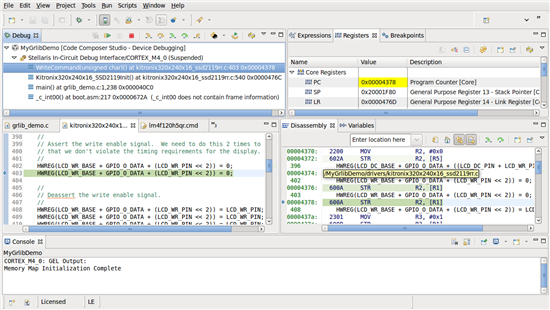

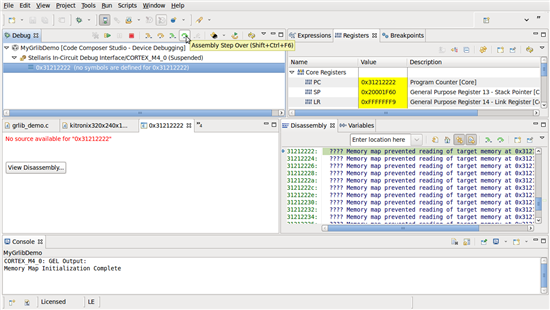

All project is included here, this is from RDMIDK example, I cannot compile full version due to licence limit, after a while I identified where code lost control, assembly step over:

First STEP

Next step crash.. Any idea why???