Other Parts Discussed in Thread: DLP3010EVM-LC, , DLPA2005, TIDA-080003

Dear Sir

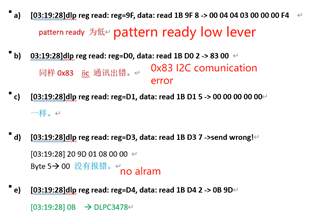

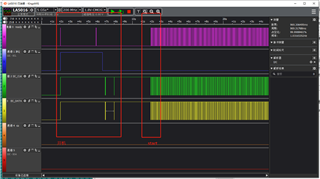

Our problem is that the projection of DLP is suspended for about two hours.The set of chipsets we use is :dlpc3478+ dlpc3010) + dlpa2005.We design the reference design to be: "tida-080003_dlp3010evm-lc_displayboard_revb."The normal time logic analyzer scan pattern_readyout host_irq, iic_clk, iic_data.

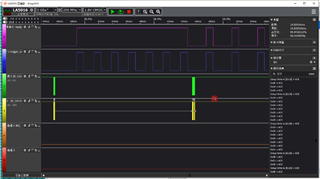

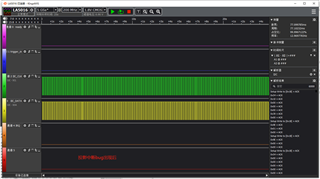

When a problem occurs, we use the logic analyzer to pick up the following signal state.

We found it is the read state register 0x9f, byte1, which indicates that the pattern ready is low; There are also registers 0x d0 byte1 for the flow 0x83' main app, and iic communication error .