Other Parts Discussed in Thread: DLPC4422, DLPDLCR660TEVM, DLPLCRDC4422EVM

Hello, TI team!

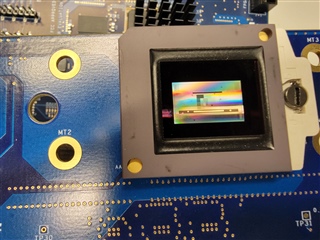

How can I correctly display DMD native resolution of 2716x1528?

I asked China's team, and they answered yes.

1. only two resolutions are supported for Vby1 input signal.

2. If it is a 3840x2160 input signal, set XPR ON UHD.

3. If it is a 2712x1528 input signal, set XPR OFF 2WAY.

Then, according to the requirements of DLP660te _ VX1 _ Input _ Video _ Timings, I input 2712x1528 signal to FPGA after booting, and then set XPR OFF 2WAY, but at this time, the DMD screen will flash or show nothing, and then enter SOLIDFIELD mode.

What I want to ask is,

1. Are my operation steps correct?

2. We have found two front-end board suppliers, whose input resolution is 3840x2160, and setting XPR ON UHD can display normally. However, if the signal is input at 2712x1528 and XPR OFF 2WAY is set, it can't be displayed correctly. Different Video_Timings parameters have been tested and modified, but it still can't be displayed correctly. Any good suggestions?

3. Why does DLP enter SOLIDFIELD mode?

4. I checked the serial port printing information. In XPR ON UHD mode, the following data is displayed:

Event: Source Stable Detected on channel

ALC: 15 4705 SD_STABLE

datapathf: Transition to ATTEMPCOMPLETE

ALC: 16 336 FR_DIGITAL_COMPLETE

ALC: 16 7234 AC_MODE_LOCKED

In XPR OFF UHD mode, the following data is displayed:

Event: Source Stable Detected on channel

ALC: 21 4691 SD_STABLE

ALC: 21 8105 FR_DIGITAL_T_LOCK

ALC: 21 12587 AC_DIGITAL_FRAMING

ALC: 21 12587 AC_DIGITAL_FRAMING

ALC: 33 257 FR_DIGITAL_FAIL

ALC: 33 4414 AC_RESTART_ALGORITHM

ALC: 33 8945 AL_CHANNEL_RESET

ALC: 34 2038 FR_DIGITAL_MEASURE

ALC: 34 6493 AC_DIGITAL_FRAMING

ALC: 34 10796 AL_MODE_DETECT

ALC: 35 257 SD_UNSTABLE

Could you please explain this mistake?

5. We also have access to related similar problems, such as e2e.ti.com/.../dlplcrdc4422evm-pattern-programming. But this can't solve my problem, because the post only stated that they solved the 4K display by adjusting the frequency, and then said that the can project 2.7K pattern successfully and turn off XPR manually in FPGA control page, but did not explain how to solve the 2.7 resolution display.

I am very grateful to TI team for helping me solve this problem.