Other Parts Discussed in Thread: TPS65100, , AM2632

Tool/software:

Hello TI,

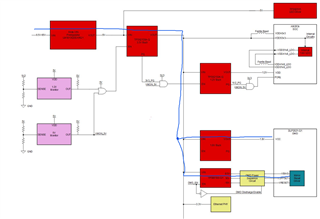

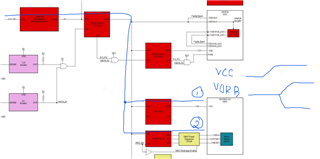

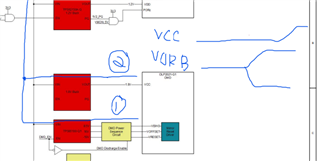

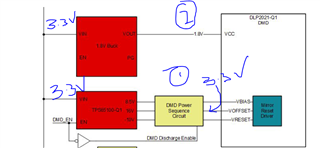

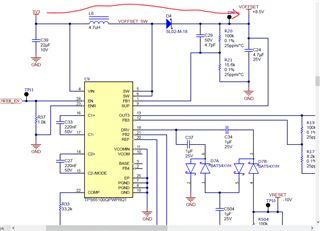

We are using LDO TPS6285018AQDRLRQ1 for 1.8V generation and TPS65100 chip for Voffset , Vbias and Vreset Voltages generation.

We have same Supply 3.3V available at input for both LDO TPS6285018AQDRLRQ1 for 1.8V generation and TPS65100 chip.

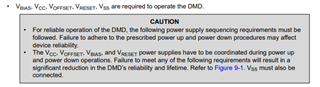

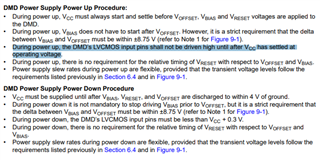

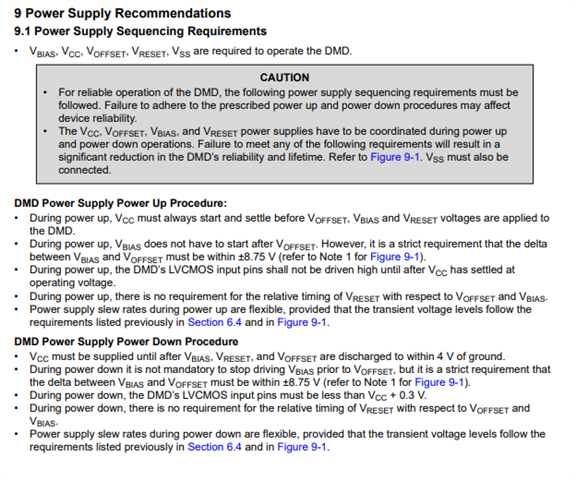

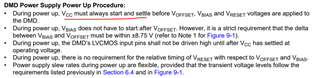

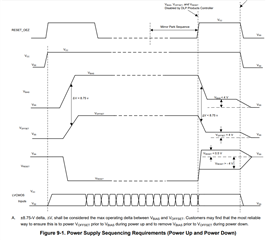

We have issue during power up sequence , that 3.3V available at Voffset before 1.8V Available , which is not as per power up sequence

Did this will be issue really issue ? I think this should not be issue.

Because , during power down sequence it mentioned that VCC 1.8V can be discharged , when Voffset , Vbias and Vreset was < 4V .

Thanks and regards

Srinath