Hi,

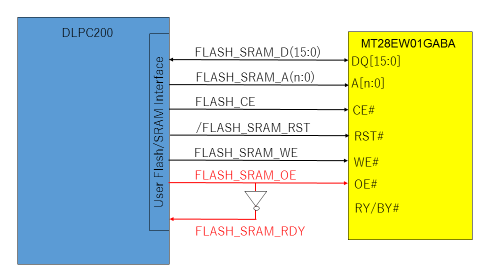

I have questions about Parallel Flash Memory Interface of DLPC200.

Q1: I want to use MT28EW01GABA1HPC memory instead of JS28F00AP30BF. Is the firmware of DLPC200 compatible?

Q2: The WAIT signal of JS28F00AP30BF is connected to FLASH_SRAM_RDY terminal.

If MT28EW01GABA1HPC is used, can I connect the RY/BY# signal of this memory to FLASH_SRAM_RDY?

Q3: Is FLASH_SRAM_RDY terminal allowed to be pulled up? Because the RY/BY# signal needs to be pulled up.

Q4: I think that the minimum value of the tAVAV described in the following document should be specified, but this document is described the maximum value. Is my thinking correct?

Q5: I'd like to verify that I can meet the requirements of tPHQV(Max:150ns) on my custom board. So, I want to know /RST the minimum time from /RST goes high to /CE goes low.

Best regards,

H.U