Other Parts Discussed in Thread: DLPLCR65NEVM, DLPC410, DLP9500, DLP650LNIR

Hello Team,

According to user manual, it guarantee 32k frame rate on DLPLCR65NEVM.

However, I found the max frame rate is about 6.8Hz when using GUI without giving dmd delay time.

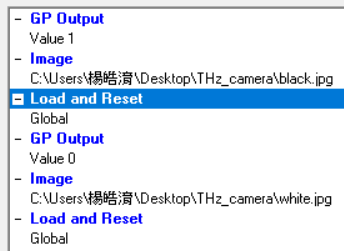

This is the setting.

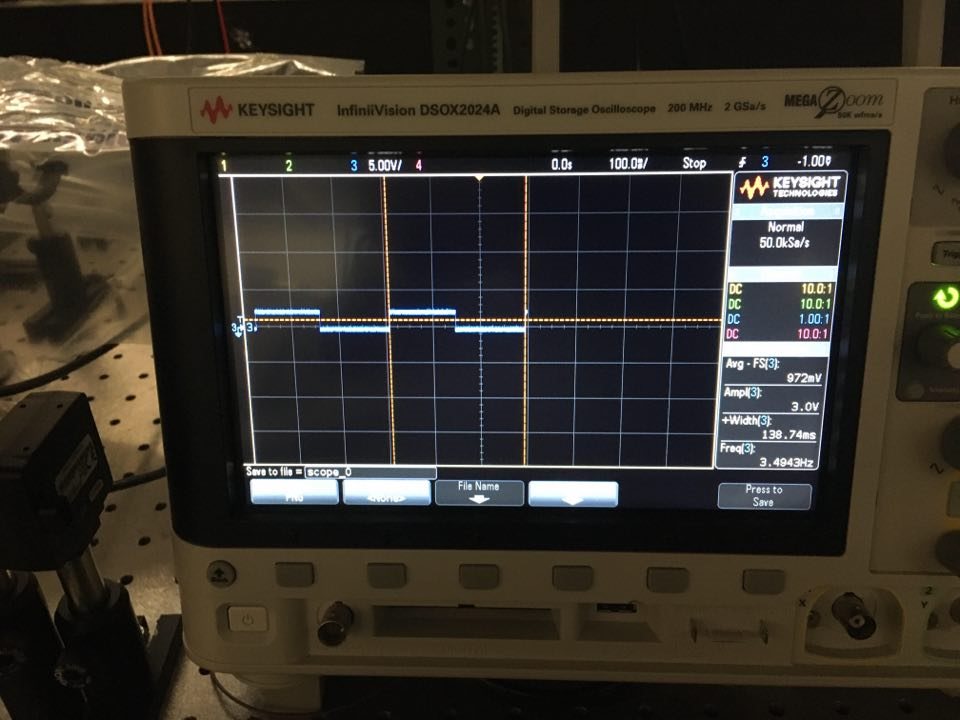

This is the output signal shown on oscilloscope.

I give dmd with two images(1 black, 1 white), and GP output is 1 and 0 respectively. That mean the real freq should be two time as shown on oscilloscope.

Please help me figure out the problem.

Mona