Hi,

we're using the DLP3478 in external pattern streaming mode. The patterns are transferred to the DLPC from an FPGA. We have a camera system to capture the projected patterns, synchronised by using the trigger out signals. The projector is not continuously streaming, we would like to project a few images/patterns in bursts, and then stop the projector between captures. Further, we run the pixel clock, PCLK, at constant frequency @148.5 MHz.

Questions:

1. Do we need to keep the VSYNC_WE running all the time, even between captures?

2. Does this also apply to the HSYNC_CS and DATAEN_CMD?

3. What is the recommended procedure for burst like operation as mentioned above? Is there a way to suspend the projector, or should we transfer 0x0 to the DLPC between the captures?

4. If we want to change the frame rate we plan to only modify the horisontal blanking, at a frame boundry, of the parallel data format sent from the FPGA to the DLPC. Would this be OK, what are the limitations regarding maximum horisontal blanking?

EDIT:

Here are two screenshots showing what we try to achieve.

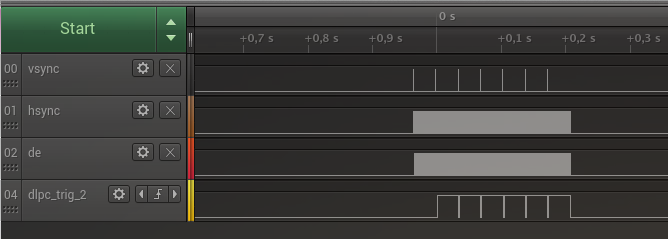

The first image is from the first capture after we power up our system.

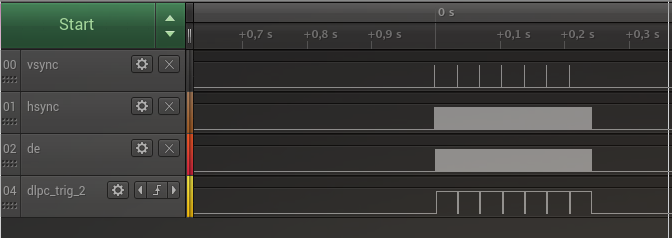

The next image shows the second capture, notice now that the dlpc_trig_2 signal asserts immediately when vsync goes high.

We would like to somehow reset the state of the DLPC such that a second capture behaves like the first capture above.

Thanks,

best regards,

Ronny