Hi, i have my own PCB with 150 Mhz versione of C5505

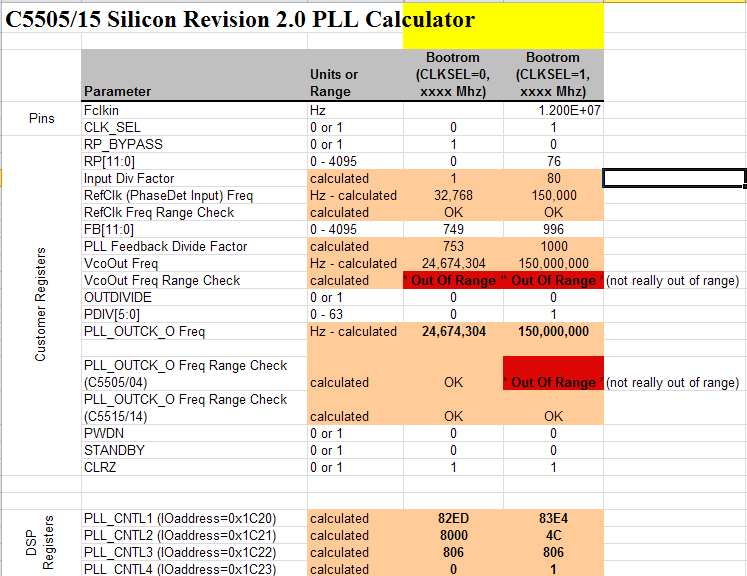

I try to configure the PLL like that:

void Init_PLL_150(void)

{

//Uint16 i;

// PLL set up from RTC

// bypass PLL

CONFIG_MSW = 0x0;

// 120 Mhz

/*

PLL_CNTL2 = 0x8000;

PLL_CNTL4 = 0x0000;

PLL_CNTL3 = 0x0806;

PLL_CNTL1 = 0x8E4A;

*/

// 150 Mhz

PLL_CNTL1 = 0x03E4;

PLL_CNTL2 = 0x004C;

PLL_CNTL3 = 0x0806;

PLL_CNTL4 = 0x0000;

while ( (PLL_CNTL3 & 0x0008) == 0);

// Switch to PLL clk

CONFIG_MSW = 0x1;

// clock gating

// enable all clocks

IDLE_PCGCR = 0x0;

IDLE_PCGCR_MSW = 0xFF84;

// reset peripherals

PER_RSTCOUNT = 0x02;

PER_RESET = 0x00fb;

for (i=0; i< 0xFFF; i++);

}

but it remains in loop in the while cycle as bolded

Why?

Thanks In advance

Paolo