Hi,

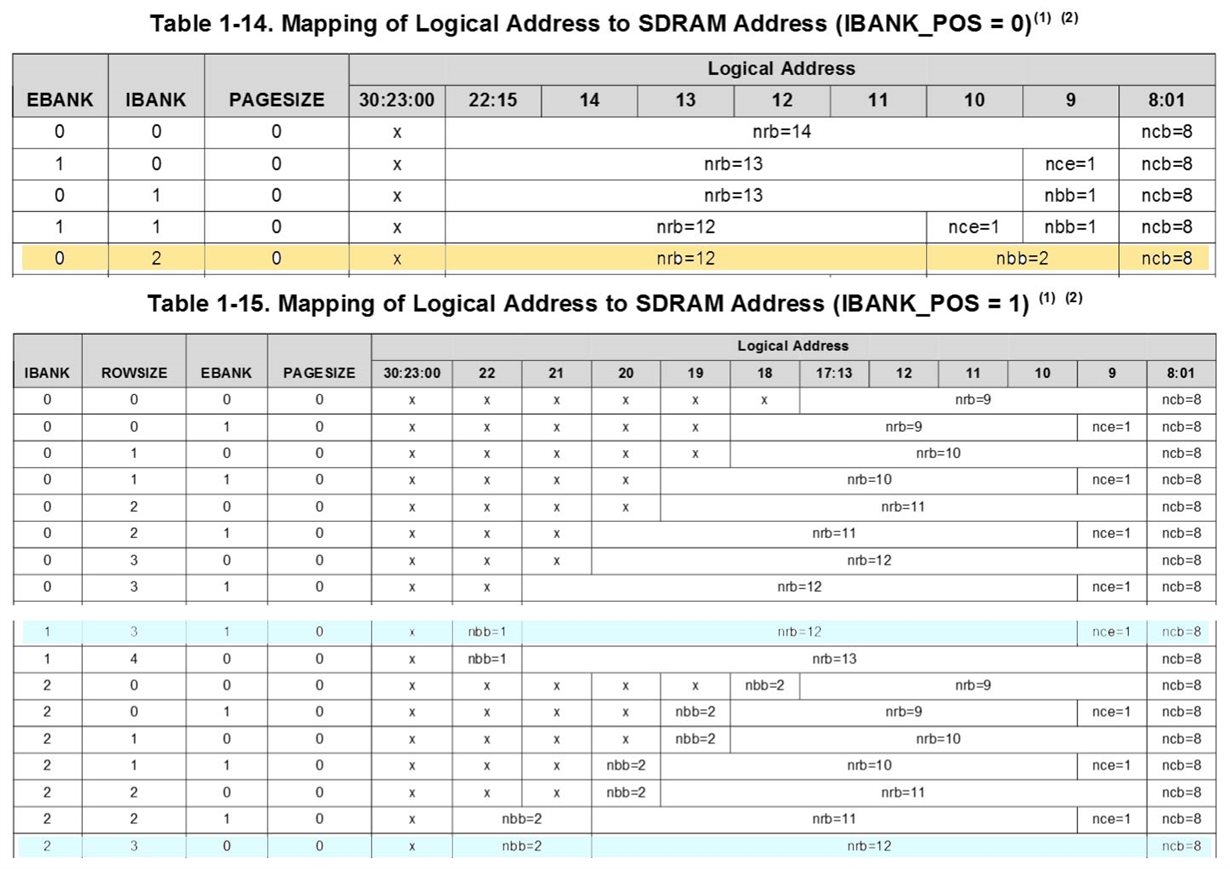

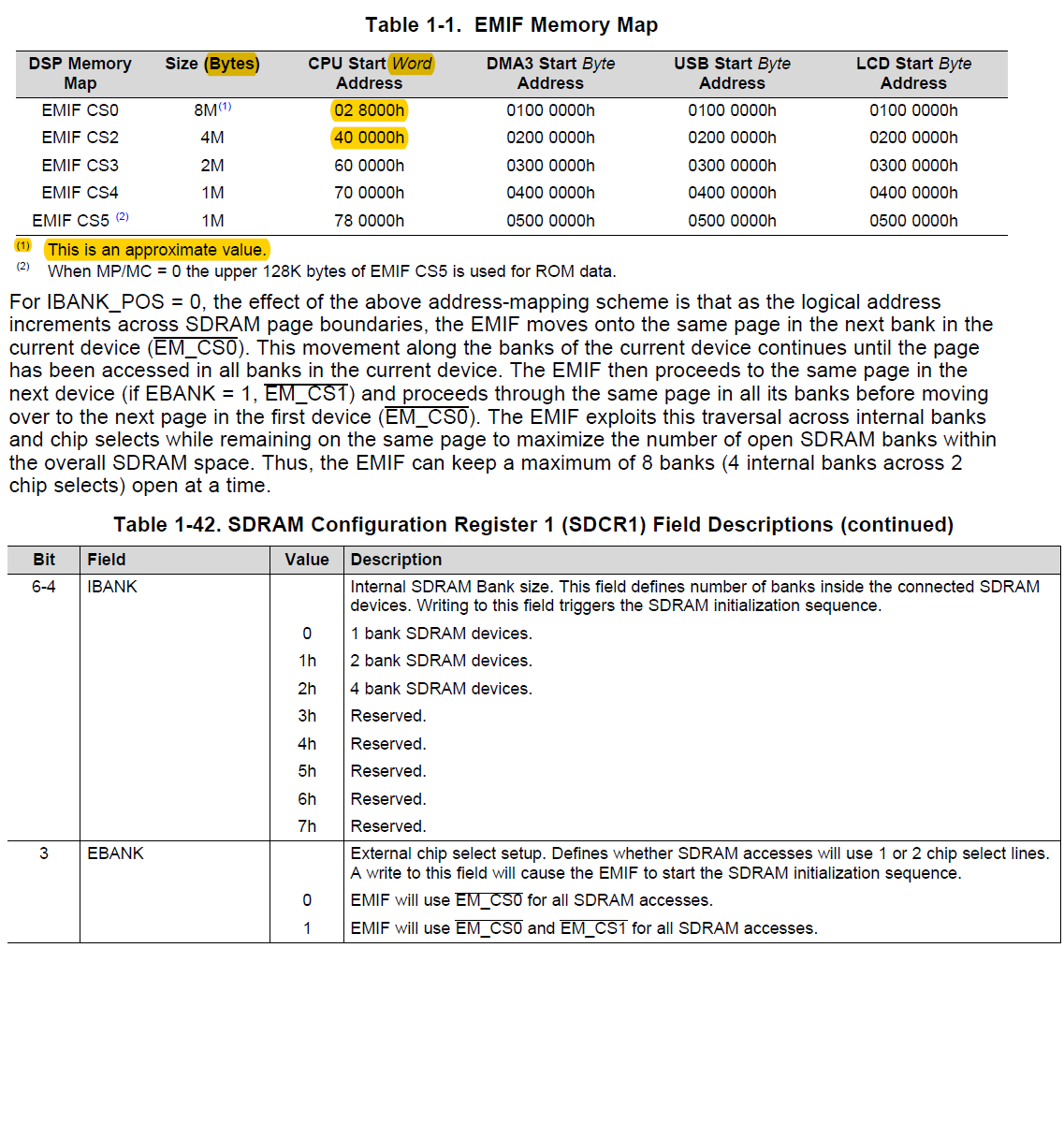

I'm having trouble with an ISSI 1MegBits x 16Bits x 4Banks (64-MBIT) SDRAM. It's organized as 4 banks of 4,096 rows by 256 columns by 16 bits, for a total of 4Meg Words (16-bit bytes for the DSP). It's being used in a custom DSP system with a 16-bit data bus and a 12-bit address bus with 2 lines for bank access of 4 banks.

The configuration and initialization seems to be correctly done, as I do the memory tests the data bus checks out OK. However the address bus tests fail and the device integrity tests fails, and these last two tests fail at the same address which turns out to be the memory address 0x3B 0000 (with the start being at 0x0 0000).

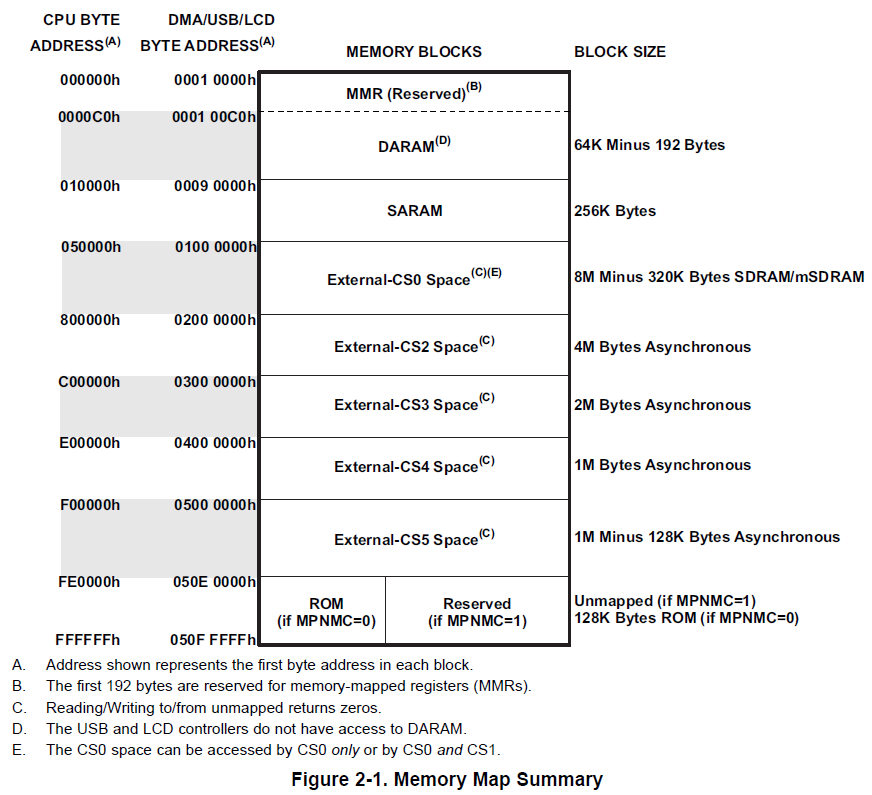

The actual DSP external memory mapping is from 0x5 0000 to 0x45 0000, but above I've subtracted the offset for simplicity. This mapping is taken from page 16 of the sprugu6b, TMS320C55xx External Memory Interface (EMIF) Users Guide.

So the DSP should be able to address beyond the 0x40 0000 DSP memory address all the way from 0x5 0000 to 0x45 0000, but it seems to fail and get stuck consistently beyond this 0x40 0000 address.

If I redefine the external memory map to be only from 0x5 0000 to 0x40 0000, and limit the tests to this memory region then obviously ALL 3 tests pass consitently. So there's the remaining 0x5 0000 (327680 or 320K) memory bytes (words) that cannot be accessed and I can't work out why this may be the case ? It's just a coincidence that this remaining 320K Words is a problem, not only on the first custom board prototype but on the second revision also ! It would appear the electrical interfacing is correct and the EMIF configuration also. Sure we could probably leave out the last 320K Words of external memory as we will never use the full 4Meg Words of external SDRAM, but it may just be something very simple that I've overlooked in the initialization or something else to do with the EMIF ?!?

BTW the SDRAM and the DSP both come in BGA packages with dense multilayer routing so access to the control lines is limited for probing without some fine soldering ... the Bank select pins are routed on the top layer so I can access these more easily ...

So my question is what could cause the memory test errors beyond the 0x40 000 memory address, which makes the SDRAM access short of 320K bytes (here a byte is 16-bits).

Thanks in advance,

Mike