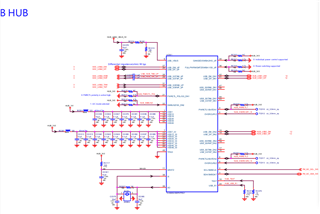

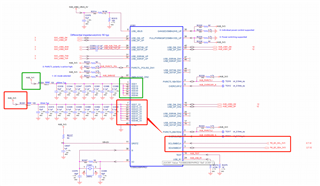

Other Parts Discussed in Thread: TUSB8020B

Hi Team,

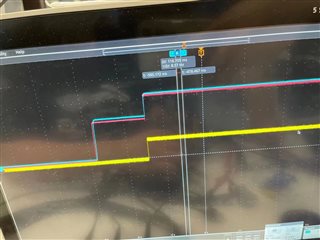

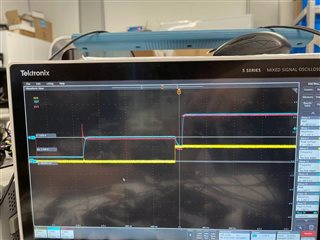

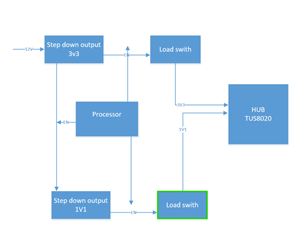

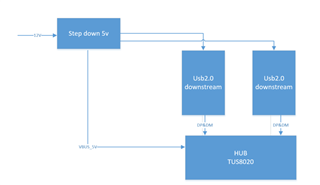

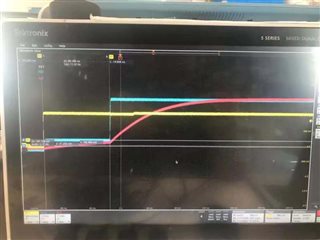

After measuring each power pin, the voltage is normal and meets the power-on sequence in the datasheet. But now the usb port is still unusable, and the usb8020 chip cannot be detected through the i2c bus, so it is suspected that the chip is not working properly.

Could you kindly give some help?