Hello TI experts,

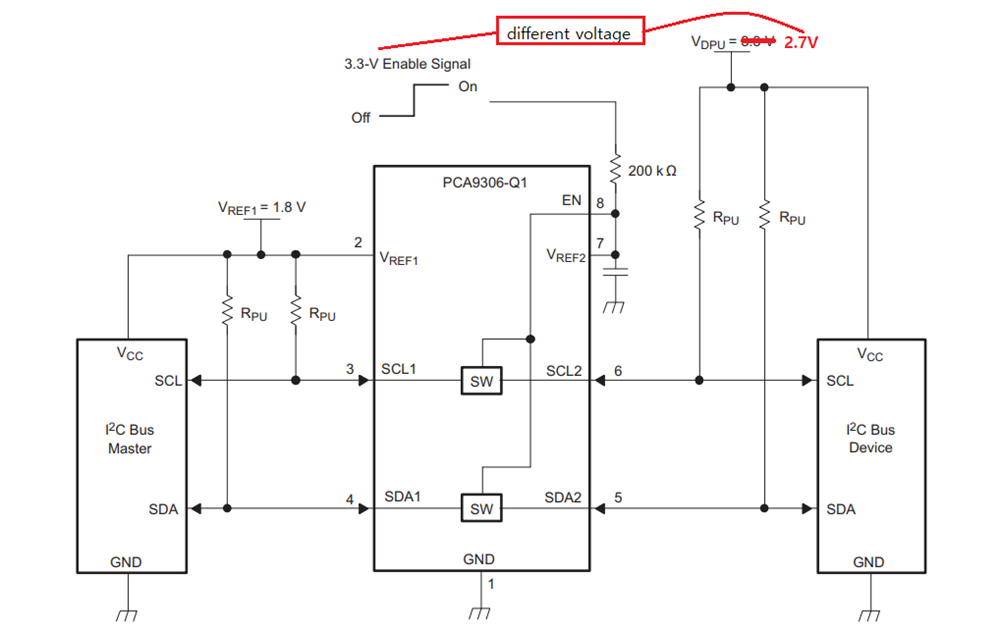

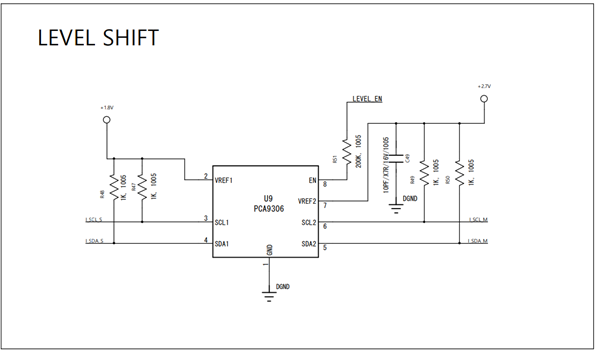

My customer drew their first schematic with PCA9306-Q1. Could you review the schematic?

and here are some question.

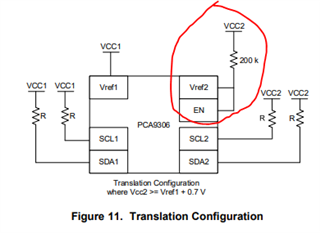

1. they wanted to separate EN and VREF2. is it possible?

they want that VREF1 and VREF2 is already powered, and only EN pin would change.

I also saw that I have to remain Hi-Z state instead of low, if I want to disable IC. (active high is fine) is it right?

2. if separation is possible, do we need to use 200kohm each of the line?

3. is there any limitation about the voltage of EN pin?

and please tell me if there are any suggestions for this schematic.

Best regards,

Chase