Dear team,

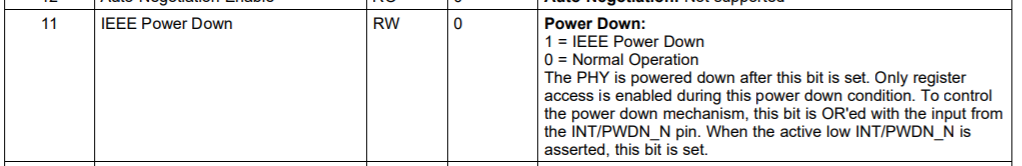

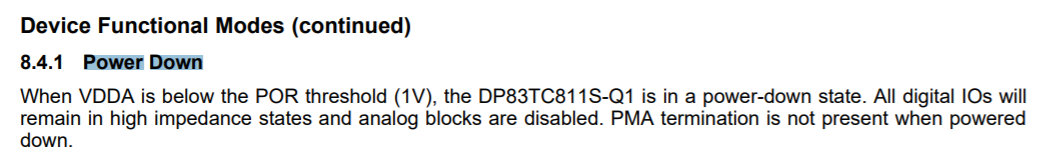

My customer asks me whether we can use register to power down our device. I found that our 0x00 bit[11]=1 means IEEE power down. I don't understand what is the difference between IEEE power down and our power down state described in 8.4.1 sector. Could you please help explain this difference?

Thanks & Best Regards,

Sherry