Hi ,

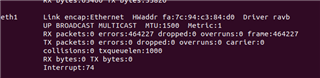

I am bringing-up DP83TG720S with Rcar H3 chip via RGMII in android 9. I referred driver for DP83TG720S at https://www.ti.com/tool/ETHERNET-SW. After adding driver, PHY linux layer adopted DP83TG720S PHY but when I try to test Digital loopback mode, all RX packets is automatically generated from PHY sent to MAC are error. When dumping pulse on RX_* pin, I saw that, RX_CTRL is always HIGH as in frames and LOW as in inter-frames. This identicates "Data Reception with Errors" but i don't know the root cause of this issue.

All register i set for Digital loopback with data generator and checker (referring to page 31: DP83TG720S-Q1 Datasheet SNLS604D – SEPTEMBER 2020 – REVISED MARCH 2021):

ret = phy_write_mmd(phydev, DP83720_DEVADDR, 0x16, 0x4);

ret = phy_write_mmd(phydev, DP83720_DEVADDR, 0x800, 0x800);

ret = phy_write_mmd(phydev, DP83720_DEVADDR, 0x0619, 0x1555);

ret = phy_write_mmd(phydev, DP83720_DEVADDR, 0x0624, 0x55BF);

Please give me some advice !