Other Parts Discussed in Thread: DS92LV0421

Hi Team,

I have two questions.

-------

[Q1]

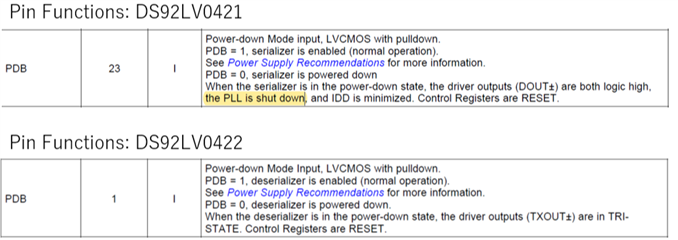

I guess that if PDB is “0”, PLL of DS92LV0422 is reset.

Is my understanding correct?

<Background to a question>

I can find “the PLL is shut down” at “Pin Functions: DS92LV0421” but can’t find “the PLL is shut down” at “Pin Functions: DS92LV0422”.

So, is there a difference between " DS92LV0421" and " DS92LV0422"?

[Q2]

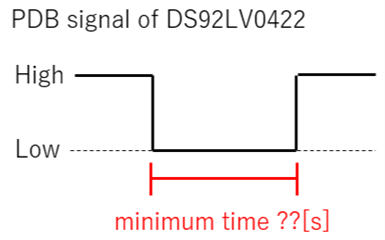

I would like to know the toggle(High -> Low -> High) timing spec of PDB.

Could you please let us know the minimum time for low period if you have any information?

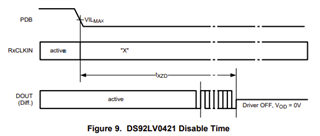

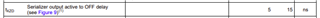

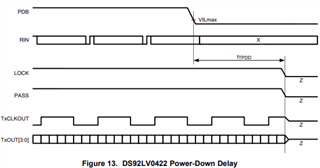

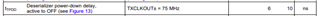

<Image>

-------

Regards,

Hide