I am using the ISO7240M as a level shifter (5V -> 3v3) as well as an isolation chip

I am also using an ISO7220M

These ISO chips provide isolation for four sADC chips (ADS7886) SPI data and control

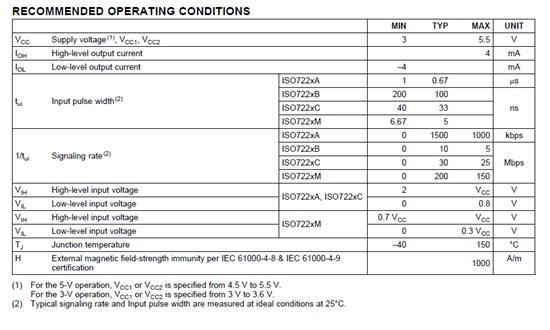

The CLK is at 6MHz and this (and CS) passes over the dual ISO7220M as expected. However the returning data does not. When I compare the input and the output of the quad 7240M there is consistantly pulses being dropped (and in extreme cases a very short (more capacitive-shaped) pulse is seen (Which then isn't valid for the LVDS drivers). Looking at the bitstream it seems the lower 30% LSB are effected, this lines up with the fact when I am measuring DClink voltage (0->600V) the output is stepping in 50V steps while the sADC output has the resolution that is expected. I have replaced the quad a couple of times just incase it was damaged.

Rails on the primary (5V) and secondary (3v3) are very solid even when data transmission is occuring. There is plenty of decoupling (10uF tant 5mm away, 100nF and 10nF ~2mm away from pins)

I am in the process of modding the card to remove the quad and use two dual's (since I know these reliably transmit the data). The quad is used on other cards in the project so I am more after any infomation as to any possible cause since this is going to have larger ramifications then just one card changing a 1x SOIC16 to 2xSOIC8 (this is before getting into sourcing and timescales)