Other Parts Discussed in Thread: TCA9617B, TMP175

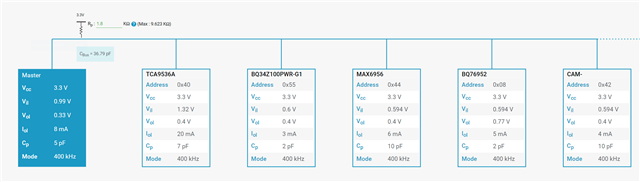

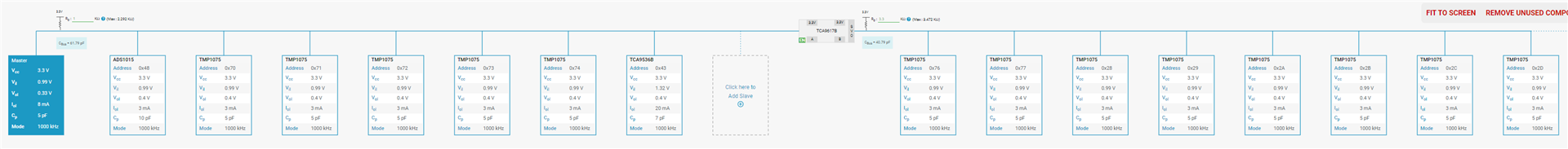

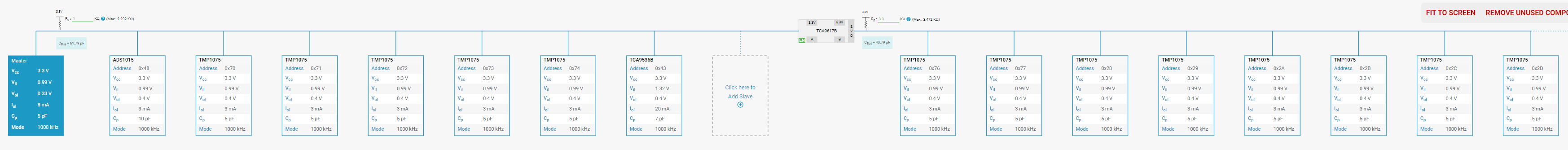

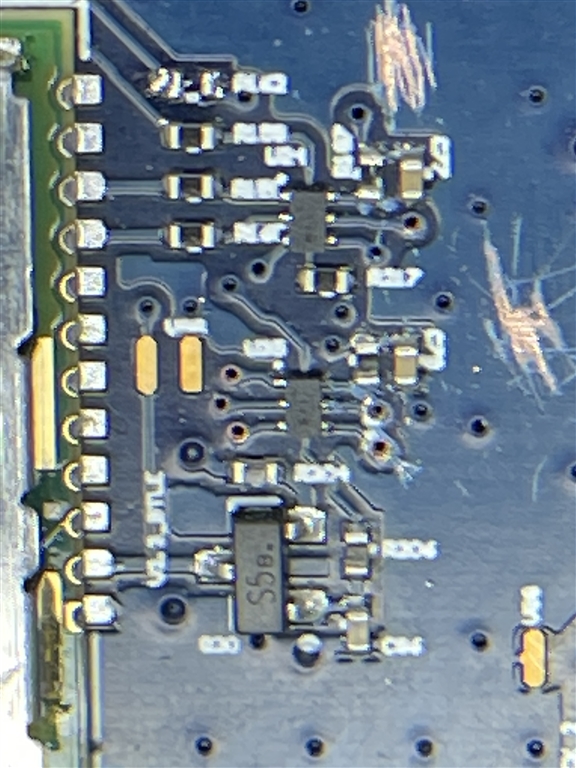

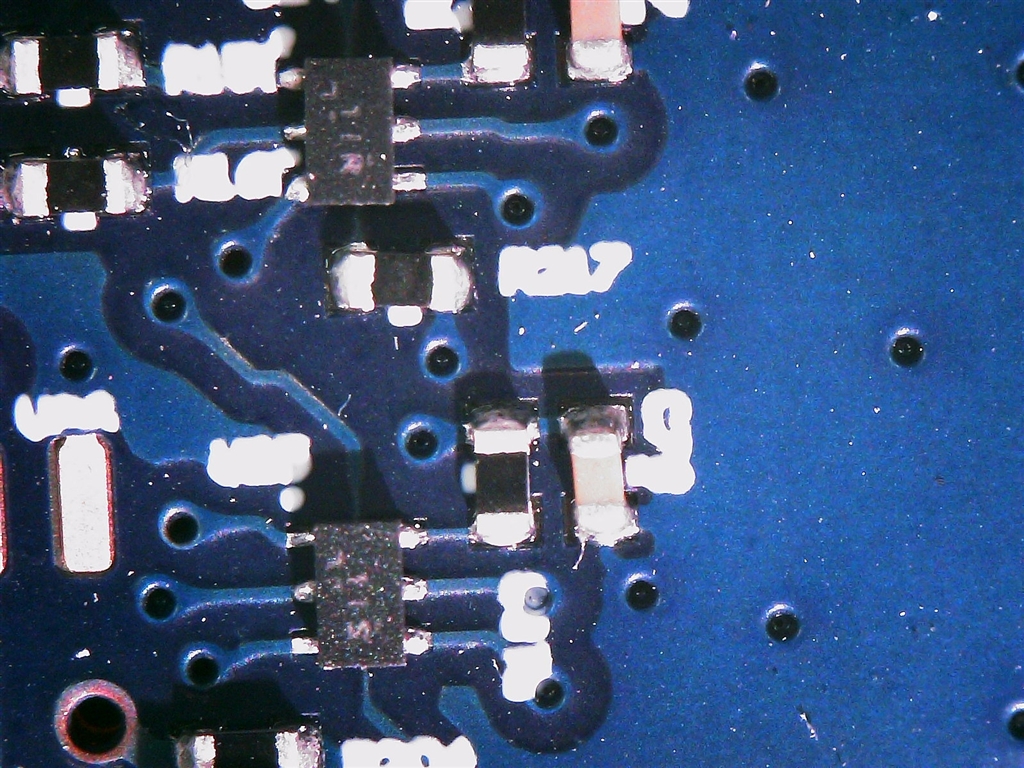

I have a TCA9536A and a TCA9536B right next to each other on the a FM+ bus. And I have another TCA9536A on a FM bus.

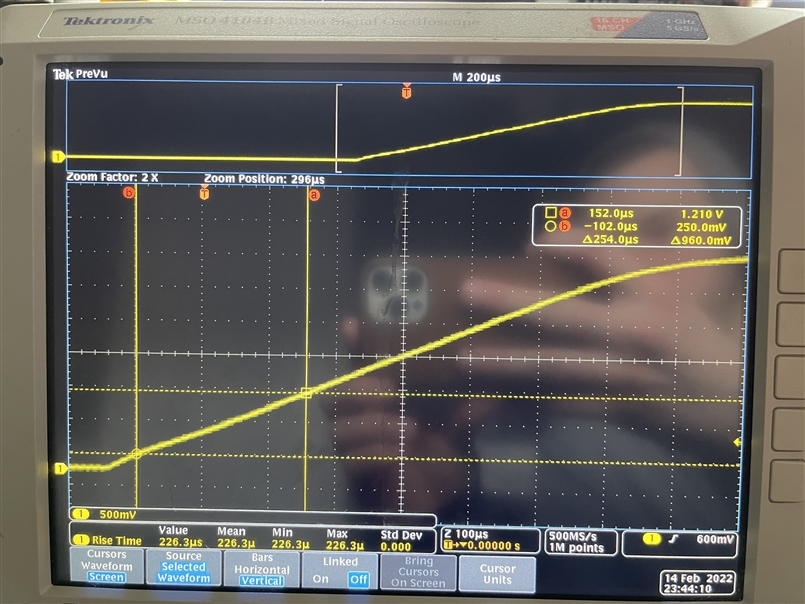

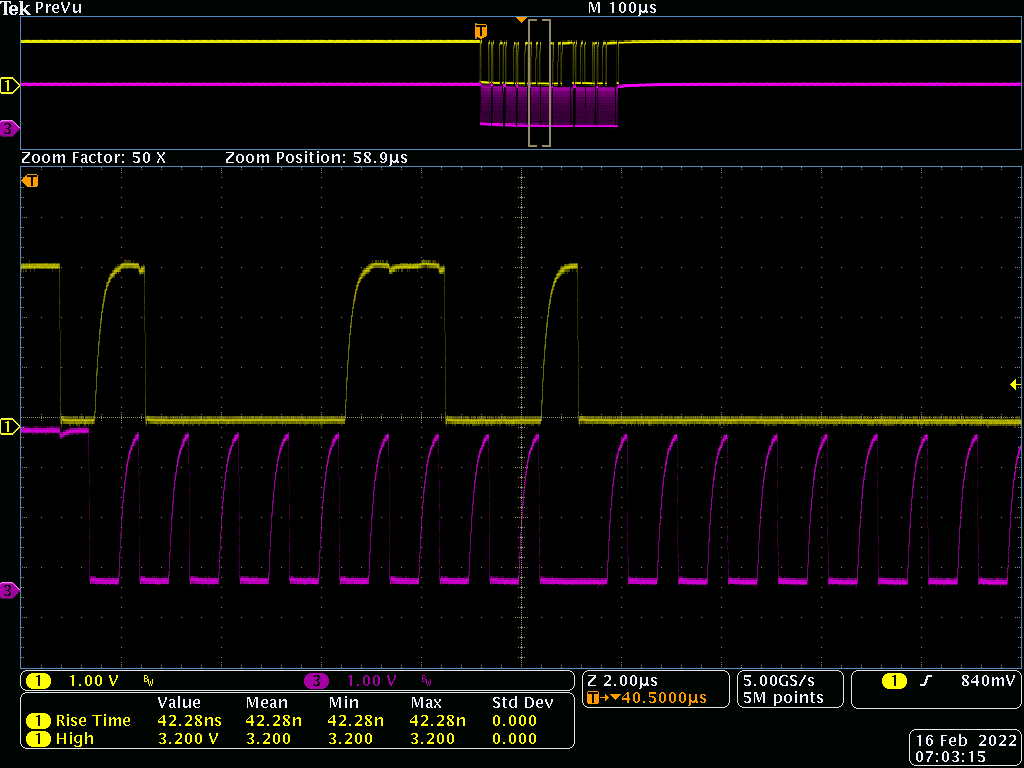

Quickly testing this prototype board I thought I was seeing communication from both the A and B on the FM+ bus; so I switched to bringing up the FM bus. But now I'm not seeing any communication from the A chip on the FM+ bus. It's possible it wasn't working the first time around.

But could you help me determine what I need to look to get this going? The "B" is responding, and I've poured over all the i2c timing and it all looks good.

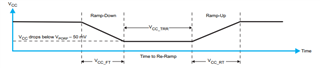

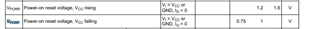

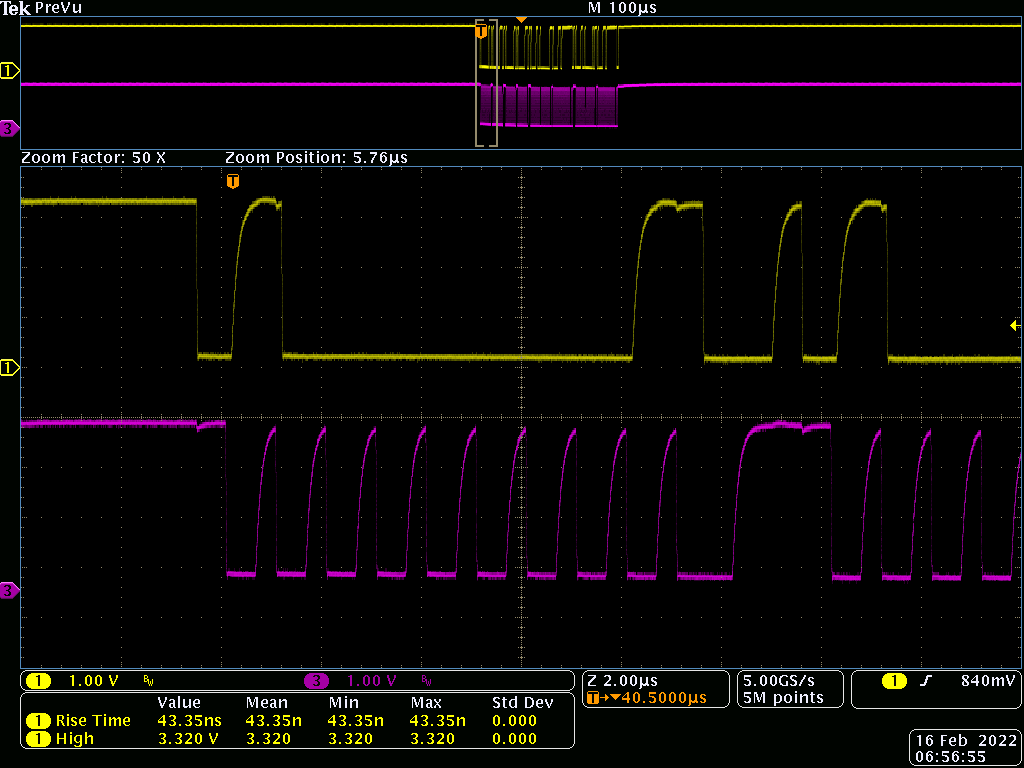

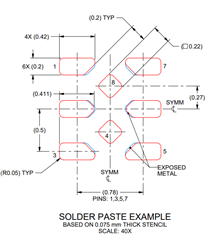

Regarding the power on ramp, what part am I needing to characterize? I'm not understanding the POR section as it doesn't clearly indicate what initial non-reset conditions should be. Vcc = 3.3V; it ramps from 0V to 1.65V in 424us, very linearly.